105

Bit 1

BSWDn1

Bit 0

BSWDn0

Description

0

0

Maximum 4 words in area n burst access

(Initial value)

1

Maximum 8 words in area n burst access

1

0

Maximum 16 words in area n burst access

1

Maximum 32 words in area n burst access

(n = 1 or 0)

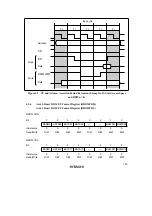

4.2.7

Bus Control Register (BCR)

Bit

15

14

13

12

11

10

9

8

BRLE

BREQOE

—

IDLC

ICIS1

ICIS0

WDBE

WAITE

Initial value

0

0

0

1

1

1

0

0

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Bit

7

6

5

4

3

2

1

0

—

—

—

—

—

—

—

—

Initial value

0

0

0

0

0

0

0

0

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

BCR is a 16-bit readable/writable register used for idle cycle settings, selection of the external bus

released state protocol, enabling or disabling of the write data buffer function, and enabling or

disabling of WAIT pin input.

BCR is initialized to H'1C00 by a reset and in hardware standby mode. It is not initialized in

software standby mode.

Bit 15—External Bus Release Enable (BRLE): Enables or disables external bus release by

means of the

BREQ

pin.

Bit 15

BRLE

Description

0

External bus release disabled

BREQ

,

BACK

, and

BREQO

pins can be used as I/O ports

(Initial value)

1

External bus release enabled

Bit 14—

BREQO

Pin Enable (BREQOE): Selects whether or not to output a signal that requests

the external bus master to drop the bus request signal (

BREQ

) in the external bus released state,

Содержание H8S/2670

Страница 5: ......

Страница 9: ......

Страница 199: ...182 ...

Страница 361: ...344 ...

Страница 393: ...376 ...

Страница 647: ...630 ...