543

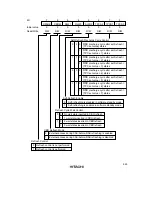

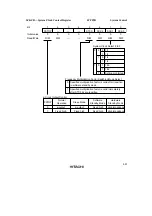

Full address mode

DMABCRL

Bit

DMABCRL

Initial value

Read/Write

7

DTME1

0

R/W

6

DTE1

0

R/W

5

DTME0

0

R/W

4

DTE0

0

R/W

3

DTIE1B

0

R/W

2

DTIE1A

0

R/W

1

DTIE0B

0

R/W

0

DTIE0A

0

R/W

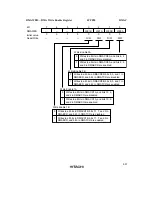

Channel 0 Data Transfer

Interrupt Enable A

0

Transfer end interrupt disabled

1

Transfer end interrupt enabled

Channel 0 Data Transfer Interrupt Enable B

0

Transfer suspended interrupt disabled

1

Transfer suspended interrupt enabled

Channel 1 Data Transfer Interrupt Enable A

0

Transfer end interrupt disabled

1

Transfer end interrupt enabled

Channel 1 Data Transfer Interrupt Enable B

0

Transfer suspended interrupt disabled

1

Transfer suspended interrupt enabled

Channel 0 Data Transfer Enable

0

Data transfer disabled

1

Data transfer enabled

Channel 1 Data Transfer Enable

0

Data transfer disabled

1

Data transfer enabled

Channel 0 Data Transfer Master Enable

0

Data transfer disabled. In burst mode,

cleared to 0 by an NMI interrupt

1

Data transfer enabled

Channel 1 Data Transfer Master Enable

0

Data transfer disabled. In burst mode,

cleared to 0 by an NMI interrupt

1

Data transfer enabled

Содержание H8S/2670

Страница 5: ......

Страница 9: ......

Страница 199: ...182 ...

Страница 361: ...344 ...

Страница 393: ...376 ...

Страница 647: ...630 ...