180

4.10.3

Bus Transfer Timing

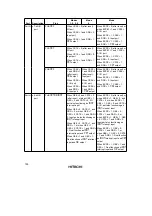

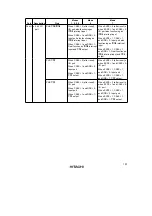

Even if a bus request is received from a bus master with a higher priority than that of the bus

master that has acquired the bus and is currently operating, the bus is not necessarily transferred

immediately. There are specific times at which each bus master can relinquish the bus.

CPU: The CPU is the lowest-priority bus master, and if a bus request is received from the DTC,

DMAC, or EXDMAC, the bus arbiter transfers the bus to the bus master that issued the request.

The timing for transfer of the bus is as follows:

•

The bus is transferred at a break between bus cycles. However, if a bus cycle is executed in

discrete operations, as in the case of a longword-size access, the bus is not transferred between

the component operations.

•

With bit manipulation instructions such as BSET and BCLR, the sequence of operations is:

data read (read), relevant bit manipulation operation (modify), write-back (write). The bus is

not transferred during this read-modify-write cycle, which is executed as a series of bus cycles.

•

If the CPU is in sleep mode, the bus is transferred immediately.

DTC: The DTC sends the bus arbiter a request for the bus when an activation request is generated.

The DTC can release the bus after a vector read, a register information read (3 states), a single data

transfer, or a register information write (3 states). It does not release the bus during a register

information read (3 states), a single data transfer, or a register information write (3 states).

DMAC: The DMAC sends the bus arbiter a request for the bus when an activation request is

generated.

In the case of an external request in short address mode or normal mode, and in cycle steal mode,

the DMAC releases the bus after a single transfer.

In block transfer mode, it releases the bus after transfer of one block, and in burst mode, after

completion of the transfer. However, in the event of an EXDMAC or external bus release request,

which have a higher priority than the DMAC, the bus may be transferred to the bus master even if

burst transfer is in progress.

EXDMAC: The EXDMAC sends the bus arbiter a request for the bus when an activation request

is generated.

As the EXDMAC is used exclusively for transfers to and from the external bus, if the bus is

transferred to the EXDMAC, internal accesses by other internal bus masters are still executed in

parallel.

In normal transfer mode or cycle steal transfer mode, the EXDMAC releases the bus after a single

transfer.

Содержание H8S/2670

Страница 5: ......

Страница 9: ......

Страница 199: ...182 ...

Страница 361: ...344 ...

Страница 393: ...376 ...

Страница 647: ...630 ...