539

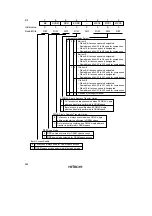

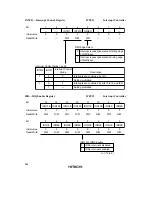

DMACR0A—DMA Control Register 0A

H'FF22

DMAC

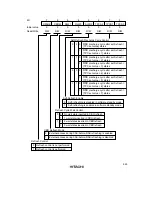

DMACR1A—DMA Control Register 1A

H'FF24

DMAC

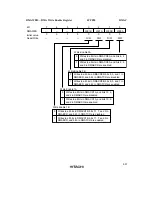

DMACR0B—DMA Control Register 0B

H'FF23

DMAC

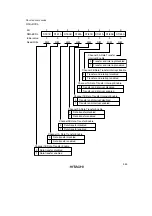

DMACR1B—DMA Control Register 1B

H'FF25

DMAC

Full address mode

DMACRA

Bit

DMACRA

Initial value

Read/Write

15

DTSZ

0

R/W

14

SAID

0

R/W

13

SAIDE

0

R/W

12

BLKDIR

0

R/W

11

BLKE

0

R/W

10

—

0

R/W

9

—

0

R/W

8

—

0

R/W

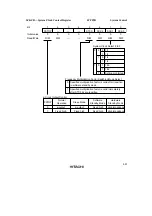

Block Direction/Block Enable

0

Transfer in normal mode

1

0

1

0

1

Transfer in block transfer mode,

destination is block area

Transfer in normal mode

Transfer in block transfer mode,

source is block area

Source Address Increment/Decrement

0

MARA is fixed

1

0

1

0

1

MARA is incremented after a data transfer

(1) When DTSZ = 0, MARA is incremented by 1 after a transfer

(2) When DTSZ = 1, MARA is incremented by 2 after a transfer

MARA is fixed

MARA is decremented after a data transfer

(1) When DTSZ = 0, MARA is decremented by 1 after a transfer

(2) When DTSZ = 1, MARA is decremented by 2 after a transfer

Data Transfer Size

0

Byte-size transfer

1

Word-size transfer

Содержание H8S/2670

Страница 5: ......

Страница 9: ......

Страница 199: ...182 ...

Страница 361: ...344 ...

Страница 393: ...376 ...

Страница 647: ...630 ...