168

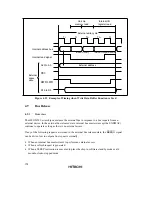

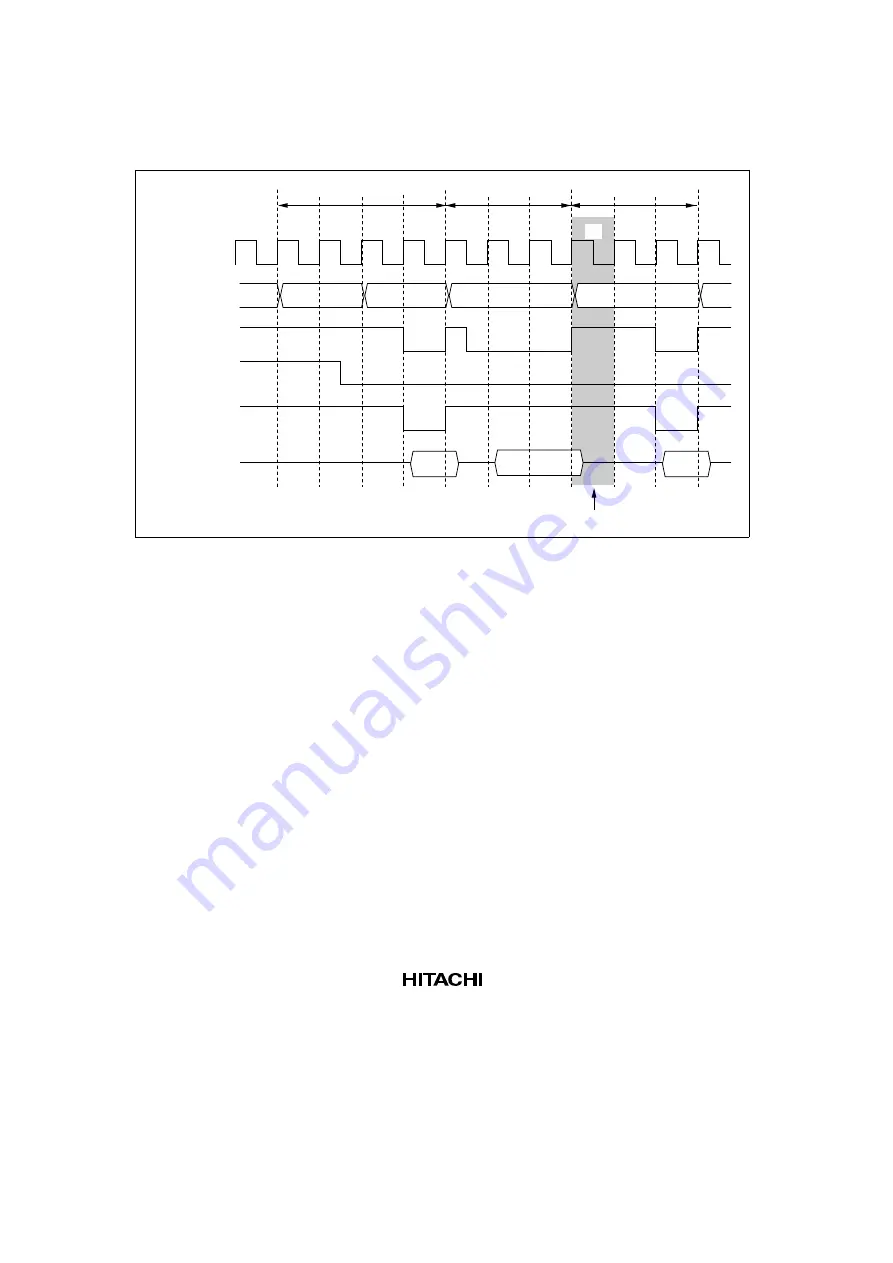

In burst access in RAS down mode, the settings of bits ICIS1, ICIS0, and IDLC are valid and an

idle cycle is inserted. The timing in this case is illustrated in figures 4.48 and 4.49.

T

p

Address bus

ø

RD

RAS

UCAS

,

LCAS

External read

Idle cycle

Data bus

T

r

T

c1

T

c2

T

1

DRAM space read

DRAM space read

T

2

T

c2

T

3

T

i

T

c1

Figure 4.48 Example of Idle Cycle Operation in RAS Down Mode (1)

(Consecutive Reads in Different Areas) (IDLC = 0, RAST = 0, CAST = 0)

Содержание H8S/2670

Страница 5: ......

Страница 9: ......

Страница 199: ...182 ...

Страница 361: ...344 ...

Страница 393: ...376 ...

Страница 647: ...630 ...