112

4.2.9

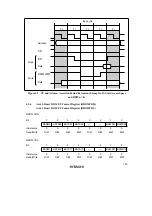

DRAM Access Control Register (DRACCR)

Bit

7

6

5

4

3

2

1

0

DRMI

—

TPC1

TPC0

—

—

RCD1

RCD0

Initial value

0

0

0

0

0

0

0

0

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

DRACCR is an 8-bit readable/writable register used to set the DRAM interface bus specifications.

DRACCR is initialized to H'00 by a reset and in hardware standby mode. It is not initialized in

software standby mode.

Bit 7—Idle Cycle Insertion (DRMI): Selects whether or not an idle cycle is inserted when a

normal access cycle follows a DRAM read cycle.

Bit 7

DRMI

Description

0

Idle cycle not inserted after DRAM space access

(Initial value)

1

Idle cycle inserted after DRAM space access

Idle cycle insertion conditions, setting of number of states, etc., comply with settings

of bits ICIS1, ICIS0, and IDLC in BCR register

Bit 6—Reserved: This is a readable/writable bit, but the write value should always be 0.

Bits 5 and 4—Precharge State Control (TPC1, TPC0): These bits select the number of states in

the RAS precharge cycle in normal access and refreshing. From 1 to 4 states can be set for the

precharge cycle.

Bit 5

TPC1

Bit 4

TPC0

Description

0

0

RAS

precharge cycle comprises 1 state

(Initial value)

1

RAS

precharge cycle comprises 2 states

1

0

RAS

precharge cycle comprises 3 states

1

RAS

precharge cycle comprises 4 states

Bits 3 and 2—Reserved: These are readable/writable bits, but the write value should always be 0.

Bits 1 and 0—RAS-CAS Wait Control (RCD1, RCD0): These bits select whether or not a wait

cycle is to be inserted between the

RAS

assert cycle and

CAS

assert cycle. A 1- to 4-state wait

cycle can be inserted.

Содержание H8S/2670

Страница 5: ......

Страница 9: ......

Страница 199: ...182 ...

Страница 361: ...344 ...

Страница 393: ...376 ...

Страница 647: ...630 ...