591

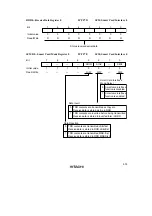

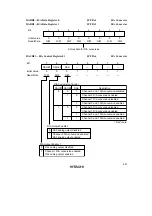

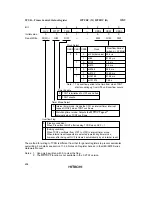

BRR2—Bit Rate Register 2

H'FF89

SCI2, Smart Card Interface 2

Bit

Initial value

Read/Write

7

1

R/W

6

1

R/W

5

1

R/W

4

1

R/W

3

1

R/W

2

1

R/W

1

1

R/W

0

1

R/W

Sets the serial transmit/receive bit rate

Note: For details see section 12.2.8, Bit Rate Register (BRR), in the H8S/2678 Series

Hardware Manual.

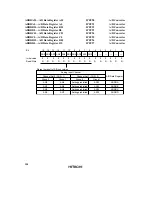

Содержание H8S/2670

Страница 5: ......

Страница 9: ......

Страница 199: ...182 ...

Страница 361: ...344 ...

Страница 393: ...376 ...

Страница 647: ...630 ...