533

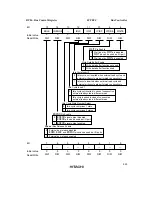

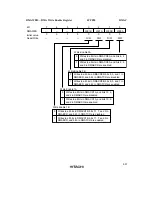

IOAR0B—I/O Address Register 0B

H'FEEC

DMAC

*

: Undefined

Bit

IOAR0B

Initial value

Read/Write

15

*

R/W

14

*

R/W

13

*

R/W

12

*

R/W

11

*

R/W

10

*

R/W

9

*

R/W

8

*

R/W

7

*

R/W

6

*

R/W

5

*

R/W

4

*

R/W

3

*

R/W

2

*

R/W

1

*

R/W

0

*

R/W

In short address mode: Specifies transfer destination/transfer source address

In full address mode:

Not used

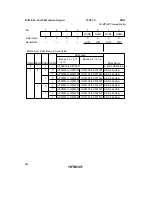

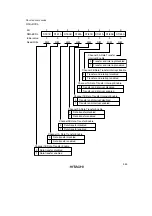

ETCR0B—Transfer Count Register 0B

H'FEEE

DMAC

*

: Undefined

Note: Not used in normal mode.

Bit

ETCR0B

Initial value

Read/Write

Sequential mode

and idle mode

Repeat mode

Block transfer mode

15

*

R/W

14

*

R/W

13

*

R/W

12

*

R/W

11

*

R/W

10

*

R/W

9

*

R/W

8

*

R/W

7

*

R/W

6

*

R/W

5

*

R/W

4

*

R/W

3

*

R/W

2

*

R/W

1

*

R/W

0

*

R/W

Transfer counter

Transfer counter

Holds number of transfers

Block transfer counter

Содержание H8S/2670

Страница 5: ......

Страница 9: ......

Страница 199: ...182 ...

Страница 361: ...344 ...

Страница 393: ...376 ...

Страница 647: ...630 ...