170

T

p

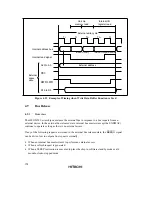

Address bus

ø

RD

RAS

UCAS

,

LCAS

External read

Idle cycle

Data bus

T

r

T

c1

T

c2

T

1

DRAM space read

DRAM space read

T

2

T

c2

T

3

T

i

T

i

T

c1

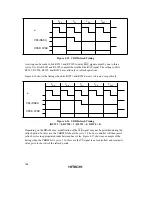

Figure 4.50 Example of Idle Cycle Operation after DRAM Access (1)

(Consecutive Reads in Different Areas) (IDLC = 0, RAST = 0, CAST = 0)

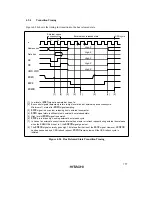

T

p

Address bus

ø

RD

RAS

HWR

,

LWR

UCAS

,

LCAS

External write

Idle cycle

Data bus

T

r

T

c1

T

c2

T

1

DRAM space read

DRAM space read

T

2

T

c2

T

3

T

i

T

c1

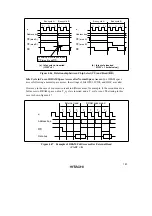

Figure 4.51 Example of Idle Cycle Operation after DRAM Access (2)

(Read after Write) (IDLC = 0, RAST = 0, CAST = 0)

Содержание H8S/2670

Страница 5: ......

Страница 9: ......

Страница 199: ...182 ...

Страница 361: ...344 ...

Страница 393: ...376 ...

Страница 647: ...630 ...