518

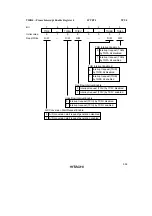

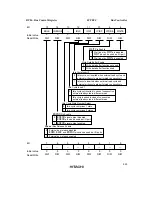

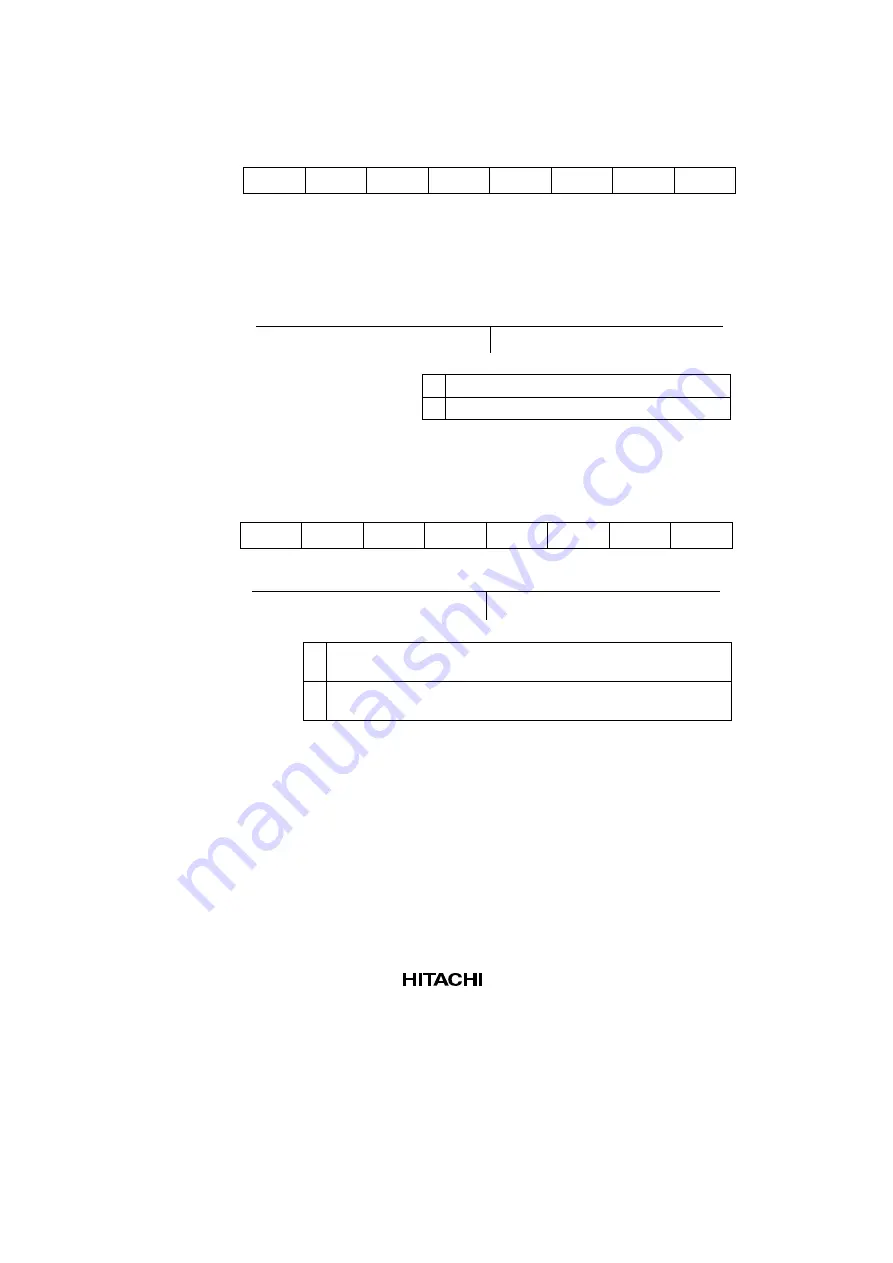

ABWCR—Bus Width Control Register

H'FEC0

Bus Controller

Bit

Modes 2, 4, 6

Initial value

Read/Write

Modes 1, 5, 7

Initial value

Read/Write

7

ABW7

1

R/W

0

R/W

6

ABW6

1

R/W

0

R/W

5

ABW5

1

R/W

0

R/W

4

ABW4

1

R/W

0

R/W

3

ABW3

1

R/W

0

R/W

2

ABW2

1

R/W

0

R/W

1

ABW1

1

R/W

0

R/W

0

ABW0

1

R/W

0

R/W

0 Area n is designated as 16-bit access space

Area n is designated as 8-bit access space

Area 7 to 0 Bus Width Control

1

(n = 15 to 0)

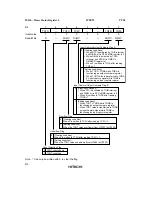

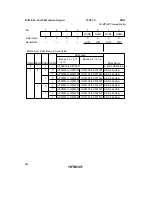

ASTCR—Access State Control Register

H'FEC1

Bus Controller

Bit

Initial value

Read/Write

7

AST7

1

R/W

6

AST6

1

R/W

5

AST5

1

R/W

4

AST4

1

R/W

3

AST3

1

R/W

2

AST2

1

R/W

1

AST1

1

R/W

0

AST0

1

R/W

0 Area n is designated as 2-state access space

Wait state insertion in area n external space accesses is disabled

Area n external space accesses are 3-state accesses

Wait state insertion in area n external space accesses is enabled

Area 7 to 0 Access State Control

1

(n = 7 to 0)

Содержание H8S/2670

Страница 5: ......

Страница 9: ......

Страница 199: ...182 ...

Страница 361: ...344 ...

Страница 393: ...376 ...

Страница 647: ...630 ...