100

RDNCR is initialized to H'00 by a reset and in hardware standby mode. It is not initialized in

software standby mode.

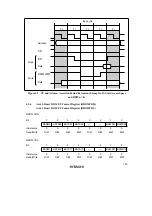

Bits 7 to 0—Read Strobe Timing Control (RDNn): As shown in figure 4.2, the read strobe for

an area for which the RDNn bit is set to 1 is negated one half-state earlier than that for an area for

which the RDNn bit is cleared to 0. The read data setup and hold time specifications are also one

half-state earlier.

The read strobe is negated one half-state earlier regardless of 2-state or 3-state access designation,

or the number of program waits.

Bit 7 to 0

RDNn

Description

0

In an area n read access, the

RD

strobe is negated at the end of the read cycle

(Initial value)

1

In an area n read access, the

RD

strobe is negated one half-state before the end of

the read cycle

(n = 7 to 0)

Bus cycle

T

1

T

2

RD

Data

RD

Data

RDNn = 0

RDNn = 1

T

3

Figure 4.2 Read Strobe Negation Timing (Example of 3-State Access Space)

Содержание H8S/2670

Страница 5: ......

Страница 9: ......

Страница 199: ...182 ...

Страница 361: ...344 ...

Страница 393: ...376 ...

Страница 647: ...630 ...