154

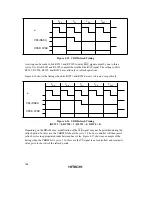

Normal space

read

DRAM space

read

T

p

T

r

T

c1

T

c2

T

1

T

2

DRAM space read

T

c1

T

c2

Note: n = 2 to 5

ø

RASn

(

CSn

)

UCAS

,

LCAS

RD

OE

Data bus

Address bus

Row address

Column address 1

Column address 2

External address

Figure 4.32 Example of Operation Timing in RAS Up Mode

(RAST = 0, CAST = 0)

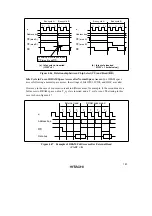

4.5.13

Refresh Control

The H8S/2678 Series is provided with a DRAM refresh control function. CAS-before-RAS (CBR)

refreshing is used.

In addition, self-refreshing can be executed when the chip enters the software standby state.

Refresh control is enabled when any area is designated as DRAM space in accordance with the

setting of bits RMTS2 to RMTS0 in the DRAMCR register.

CAS-before-RAS (CBR) Refreshing: To select CBR refreshing, set the RFSHE bit to 1 in

DRAMCR.

With CBR refreshing, RTCNT counts up using the input clock selected by bits RTCK2 to RTCK0

in REFCR, and when the count matches the value set in RTCOR (compare match), refresh control

is performed. At the same time, RTCNT is reset and starts counting up again from H'00.

Содержание H8S/2670

Страница 5: ......

Страница 9: ......

Страница 199: ...182 ...

Страница 361: ...344 ...

Страница 393: ...376 ...

Страница 647: ...630 ...