162

4.6

Burst ROM Interface

4.6.1

Overview

In the H8S/2678 Series, external space areas 0 and 1 can be designated as burst ROM space, and

burst ROM interfacing performed. The burst ROM space interface enables ROM with burst access

capability to be accessed at high speed.

Areas 1 and 0 can be designated as burst ROM space by means of bits BSRM1 and BSRM0 in

BROMCR. Consecutive burst accesses of a maximum or 4, 8, 16, or 32 words can be performed,

according to the BROMCR register setting. From 1 to 8 states can be selected for burst access.

Settings can be made independently for area 0 and area 1.

In burst ROM interface space, burst access covers only CPU read accesses.

4.6.2

Basic Timing

The number of states in the initial cycle (full access) on the burst ROM interface is determined by

the basic bus interface settings in the ASTCR, ABWCR, WTCRA, WTCRB, and CSACRH

registers. When area 0 or area 1 is designated as burst ROM interface space, the settings in the

RDCNR and CSACRL registers are ignored.

From 1 to 8 states can be selected for the burst cycle, according to the settings of bits BSTS02 to

BSTS00 and BSTS12 to BSTS10 in BROMCR. Wait states cannot be inserted. Burst access of up

to 32 words is performed, according to the settings of bits BSTS01, BSTS00, BSTS11, and

BSTS10 in BROMCR

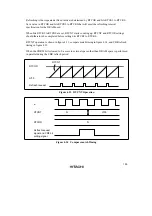

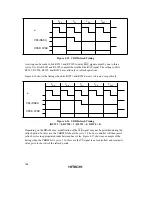

The basic access timing for burst ROM space is shown in figures 4.42 and 4.43. Figure 4.42 shows

the timing when ASTn = 1 and a 2-state burst cycle is set, and figure 4.43 shows the timing when

ASTn = 0 and a 1-state burst cycle is set.

Содержание H8S/2670

Страница 5: ......

Страница 9: ......

Страница 199: ...182 ...

Страница 361: ...344 ...

Страница 393: ...376 ...

Страница 647: ...630 ...