106

when an internal bus master performs an external space access, or when a refresh request is

generated.

Bit 14

BREQOE

Description

0

BREQO

output disabled

BREQO

pin can be used as I/O port

(Initial value)

1

BREQO

output enabled

Bit 13—Reserved: This is a readable/writable bit, but the write value should always be 0.

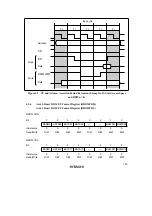

Bit 12—Idle Cycle State Number Select (IDLC): Selects the number of states in the idle cycle

set by ICIS1 and ICIS0.

Bit 12

IDLC

Description

0

Idle cycle comprises 1 state

1

Idle cycle comprises 2 states

(Initial value)

Bit 11—Idle Cycle Insert 1 (ICIS1): When consecutive external read cycles are performed in

different areas, an idle cycle can be inserted between the bus cycles. When this bit is set to 1, an

idle cycle is inserted in the case of consecutive external read cycles in different areas.

Bit 11

ICIS1

Description

0

Idle cycle not inserted in case of consecutive external read cycles in different areas

1

Idle cycle inserted in case of consecutive external read cycles in different areas

(Initial value)

Bit 10—Idle Cycle Insert 0 (ICIS0): When an external read cycle and external write cycle are

performed consecutively, an idle cycle can be inserted between the bus cycles. When this bit is set

to 1, an idle cycle is inserted when an external read cycle and external write cycle are performed

consecutively.

Bit 10

ICIS0

Description

0

Idle cycle not inserted when external read cycle and external write cycle are

performed consecutively

1

Idle cycle inserted when external read cycle and external write cycle are performed

consecutively

(Initial value)

Содержание H8S/2670

Страница 5: ......

Страница 9: ......

Страница 199: ...182 ...

Страница 361: ...344 ...

Страница 393: ...376 ...

Страница 647: ...630 ...