362

6.9

Serial Communication Interface

6.9.1

Features

•

Three independent on-chip channels in the H8S/2678 Series

•

Selection of synchronous or asynchronous serial communication mode

•

Full-duplex communication capability

•

Selection of LSB-first or MSB-first transfer

•

Built-in baud rate generator allows any bit rate to be selected

•

Selection of transmit/receive clock source

•

DTC and DMAC can be activated by four interrupts (ERI, RXI, TXI, and TEI)

•

Module stop mode can be set

6.9.2

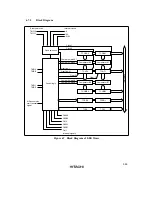

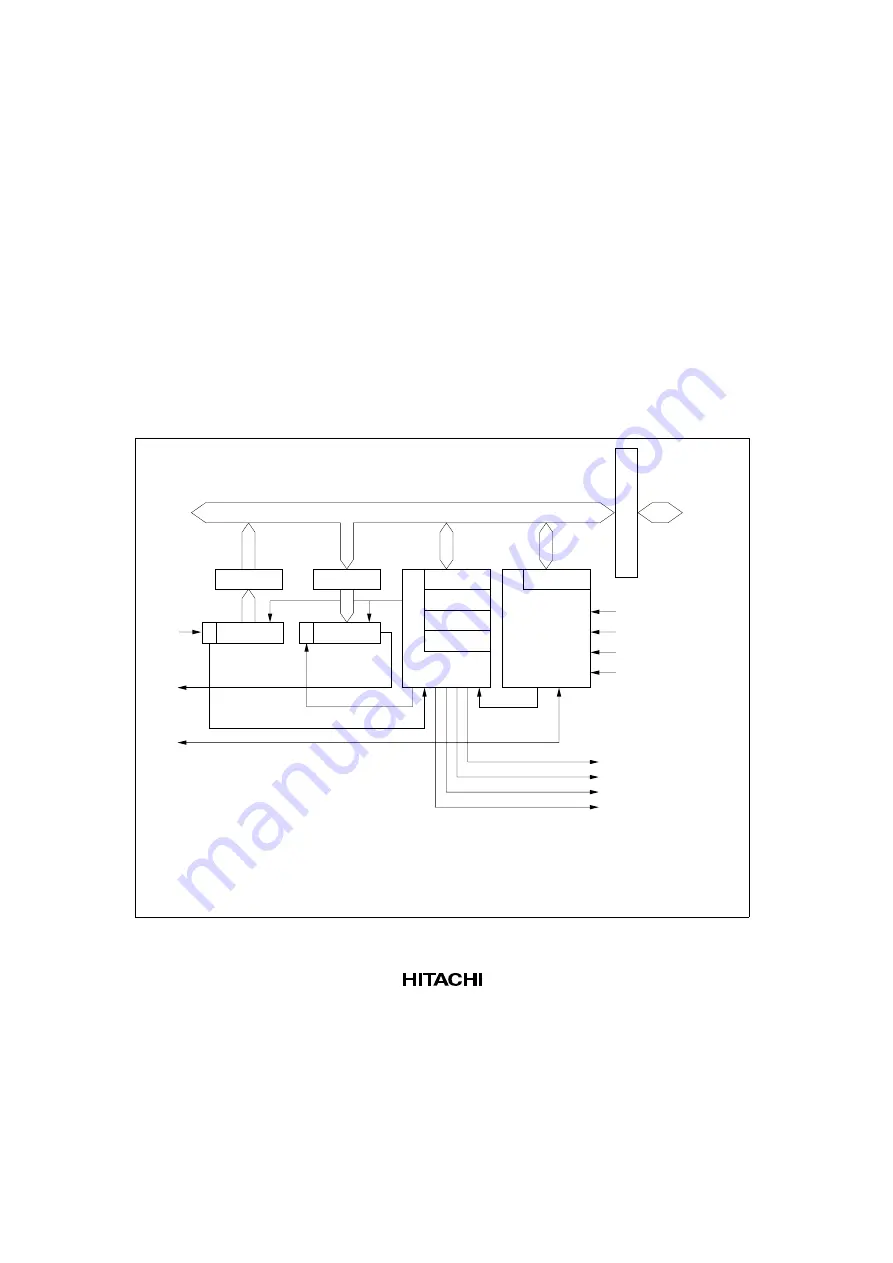

Block Diagram

RxD

TxD

SCK

Clock

ø

ø/4

ø/16

ø/64

TEI

TXI

RXI

ERI

SCMR

SSR

SCR

SMR

Transmission/

reception control

Baud rate

generator

BRR

Module data bus

Bus interface

Internal

data bus

RDR

TSR

RSR

Parity generation

TDR

Legend

SCMR: Smart card mode register

RSR:

Receive shift register

RDR:

Receive data register

TSR:

Transmit shift register

TDR:

Transmit data register

SMR:

Serial mode register

SCR:

Serial control register

SSR:

Serial status register

BRR:

Bit rate register

External clock

Parity check

Figure 6.9 Block Diagram of SCI

Содержание H8S/2670

Страница 5: ......

Страница 9: ......

Страница 199: ...182 ...

Страница 361: ...344 ...

Страница 393: ...376 ...

Страница 647: ...630 ...