375

6.16

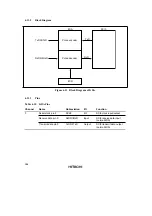

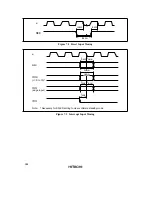

Clock Pulse Generator

6.16.1

Features

•

Comprises an oscillator, PLL (phase-locked loop) circuit, and frequency divider

•

Generates system clock (ø) and internal clock

6.16.2

Block Diagram

EXTAL

XTAL

PLL circuit

(

×

1,

×

2,

×

4)

Oscillator

Frequency

divider

System clock

To ø pin

Internal clock

To on-chip

supporting

modules

SCK2 to SCK0

SCKCR

STC0, STC1

PLLCR

Figure 6.17 Block Diagram of Clock Pulse Generator

Содержание H8S/2670

Страница 5: ......

Страница 9: ......

Страница 199: ...182 ...

Страница 361: ...344 ...

Страница 393: ...376 ...

Страница 647: ...630 ...