98

ASTCR sets the number of access states for the external memory space. The number of access

states for on-chip memory and internal I/O registers is fixed regardless of the settings in ASTCR.

ASTCR is initialized to H'FF by a reset and in hardware standby mode. It is not initialized in

software standby mode.

Bits 7 to 0—Area 7 to 0 Access State Control (AST7 to AST0): These bits select whether the

corresponding area is to be designated as 2-state access space or 3-state access space.

Wait state insertion is enabled or disabled at the same time.

Bit n

ASTn

Description

0

Area n is designated as 2-state access space

Wait state insertion in area n external space access is disabled

1

Area n is designated as 3-state access space

(Initial value)

Wait state insertion in area n external space access is enabled

(n = 7 to 0)

4.2.3

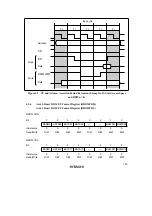

Wait Control Registers A and B (WTCRA, WTCRB)

WTCRA and WTCRB are 16-bit readable/writable registers that select the number of program

wait states for each area.

Program waits are not inserted in on-chip memory or internal I/O register access.

WTCRA and WTCRB are initialized to H'7777 by a reset and in hardware standby mode. They

are not initialized in software standby mode.

WTCRA

Bit

15

14

13

12

11

10

9

8

—

W72

W71

W70

—

W62

W61

W60

Initial value

0

1

1

1

0

1

1

1

Read/Write

R

R/W

R/W

R/W

R

R/W

R/W

R/W

Bit

7

6

5

4

3

2

1

0

—

W52

W51

W50

—

W42

W41

W40

Initial value

0

1

1

1

0

1

1

1

Read/Write

R

R/W

R/W

R/W

R

R/W

R/W

R/W

Содержание H8S/2670

Страница 5: ......

Страница 9: ......

Страница 199: ...182 ...

Страница 361: ...344 ...

Страница 393: ...376 ...

Страница 647: ...630 ...