113

Bit 1

RCD1

Bit 0

RCD0

Description

0

0

Wait cycle not inserted between

RAS

assert cycle and

CAS

assert

cycle

(Initial value)

1

1-state wait cycle inserted between

RAS

assert cycle and

CAS

assert

cycle

1

0

2-state wait cycle inserted between

RAS

assert cycle and

CAS

assert

cycle

1

3-state wait cycle inserted between

RAS

assert cycle and

CAS

assert

cycle

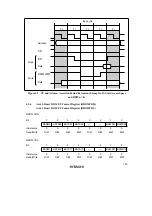

4.2.10

Refresh Control Register (REFCR)

Bit

15

14

13

12

11

10

9

8

CMF

CMIE

RCW1

RCW0

—

RTCK2

RTCK1

RTCK0

Initial value

0

0

0

0

0

0

0

0

Read/Write

R/W

*

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Bit

7

6

5

4

3

2

1

0

RFSHE

CBRM

RLW1

RLW0

SLFRF

TPCS2

TPCS1

TPCS0

Initial value

0

0

0

0

0

0

0

0

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Note:

*

Only 0 can be written, to clear the flag.

REFCR is a 16-bit readable/writable register that specifies DRAM interface refresh control.

REFCR is initialized to H'0000 by a reset and in hardware standby mode. It is not initialized in

software standby mode.

Bit 15—Compare match Flag (CMF): Status flag that indicates a match between the values of

the refresh counter (RTCNT) and the refresh time constant register (RTCOR).

Содержание H8S/2670

Страница 5: ......

Страница 9: ......

Страница 199: ...182 ...

Страница 361: ...344 ...

Страница 393: ...376 ...

Страница 647: ...630 ...