499

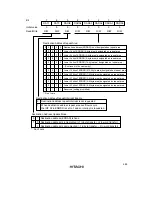

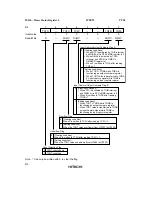

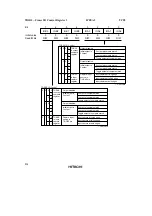

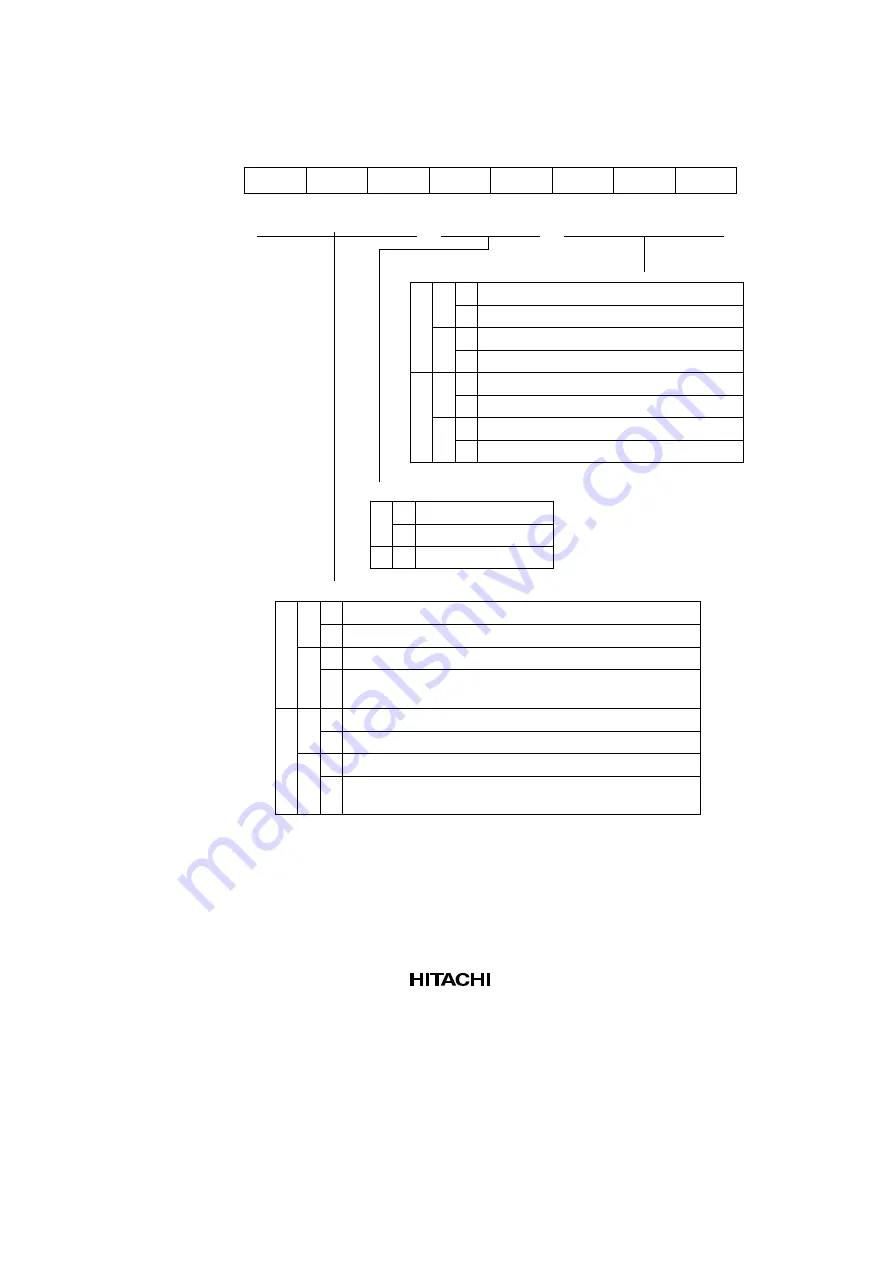

TCR3—Timer Control Register 3

H'FE80

TPU3

Bit

Initial value

Read/Write

7

CCLR2

0

R/W

6

CCLR1

0

R/W

5

CCLR0

0

R/W

4

CKEG1

0

R/W

3

CKEG0

0

R/W

2

TPSC2

0

R/W

1

TPSC1

0

R/W

0

TPSC0

0

R/W

0

1

0

1

0

1

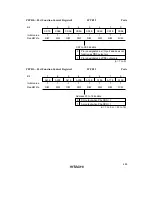

Internal clock: count on ø/1

Internal clock: count on ø/4

Internal clock: count on ø/16

Internal clock: count on ø/64

External clock: count on TCLKA pin input

Internal clock: count on ø/1024

Internal clock: count on ø/256

Internal clock: count on ø/4096

Timer Prescaler

0

1

0

1

0

1

0

1

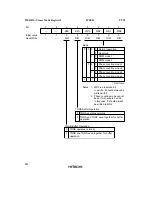

0

1

0

1

—

Count at rising edge

Count at falling edge

Count at both edges

Clock Edge

0

0

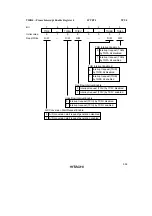

TCNT clearing disabled

TCNT cleared by TGRA compare match/input capture

TCNT cleared by TGRB compare match/input capture

Counter Clear

0

1

1

0

1

1

0

0

1

1

0

1

TCNT cleared by counter clearing for another channel

performing synchronous clearing/synchronous operation

*

1

TCNT clearing disabled

TCNT cleared by TGRC compare match/input capture

*

2

TCNT cleared by TGRD compare match/input capture

*

2

TCNT cleared by counter clearing for another channel

performing synchronous clearing/synchronous operation

*

1

Notes: 1. Synchronous operation is selected by setting the SYNC bit

in TSYR to 1.

2. When TGRC or TGRD is used as a buffer register, TCNT is

not cleared because the buffer register setting has priority,

and compare match/input capture does not occur.

Содержание H8S/2670

Страница 5: ......

Страница 9: ......

Страница 199: ...182 ...

Страница 361: ...344 ...

Страница 393: ...376 ...

Страница 647: ...630 ...