460

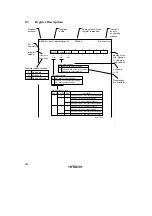

MRB—DTC Mode Register B

H'BC00 to H'BFFF

DTC

Bit

Initial value

Read/Write

7

CHNE

Undefined

—

6

DISEL

Undefined

—

5

CHNS

Undefined

—

4

—

Undefined

—

3

—

Undefined

—

2

—

Undefined

—

1

—

Undefined

—

0

—

Undefined

—

0 After a data transfer ends, the CPU interrupt is disabled

unless the transfer counter is 0

After a data transfer ends, the CPU interrupt is enabled

DTC Interrupt Select

1

0 DTC data transfer finished (waiting for activation)

DTC chain transfer (new register information is read,

and data transfer performed)

DTC Chain Transfer Enable

1

Reserved bits

(write 0)

DTC Chain Transfer Select

CHNE

0

Description

1

1

CHNS

—

0

1

No chain transfer (activation-standby

state entered at end of DTC data transfer)

Chain transfer every time

Chain transfer only when transfer counter = 0

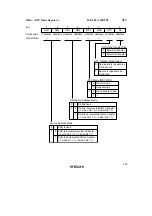

SAR—DTC Source Address Register

H'BC00 to H'BFFF

DTC

Bit

Initial value

Read/Write

23

*

—

22

*

—

21

*

—

20

*

—

19

*

—

- - -

- - -

- - -

- - -

4

*

—

3

*

—

2

*

—

1

*

—

0

*

—

Specifies data transfer source address

*

: Undefined

Содержание H8S/2670

Страница 5: ......

Страница 9: ......

Страница 199: ...182 ...

Страница 361: ...344 ...

Страница 393: ...376 ...

Страница 647: ...630 ...