144

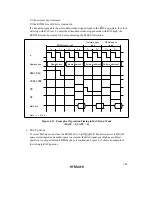

If a row address hold time or read access time is necessary, making a setting in bits RCD1 and

RCD0 in the DRACCR register allows from one to three T

rw

states, in which row address output is

maintained, to be inserted between the T

r

cycle, in which the

RAS

signal goes low, and the T

c1

cycle, in which the column address is output. Use the setting that gives the optimum row address

signal hold time relative to the fall of the

RAS

signal according to the DRAM connected and the

operating frequency of the chip. Figure 4.23 shows an example of the timing when one T

rw

state is

set.

T

p

ø

RASn

(

CSn

)

Read

Write

UCAS

,

LCAS

WE

(

HWR

)

OE

(

RD

)

Data bus

WE

(

HWR

)

OE

(

RD

)

Data bus

Address bus

T

r

T

rw

T

c1

T

c2

Row address

Column address

High

High

Note: n = 2 to 5

Figure 4.23 Example of Timing with One Row Address Output Maintenance State

(RAST = 0, CAST = 0)

Содержание H8S/2670

Страница 5: ......

Страница 9: ......

Страница 199: ...182 ...

Страница 361: ...344 ...

Страница 393: ...376 ...

Страница 647: ...630 ...