CHAPTER 10 SERIAL INTERFACE FUNCTION

User’s Manual U15195EJ5V0UD

422

(3) Continuous transmission operation

UART0 can write the next transmit data to the TXB0 register at the timing that the transmit shift register starts

the shift operation. This enables an efficient transmission rate to be realized by continuously transmitting

data even during the servicing of the transmission completion interrupt (INTST0) after the transmission of one

data frame. In addition, reading the TXSF0 bit of the ASIF0 register after the generation of an INTST0 signal

enables the TXB0 register to be efficiently written twice (2 bytes) without waiting for the transmission of 1 data

frame.

When continuous transmission is performed, data should be written after referencing the ASIF0 register to

confirm the transmission status and whether or not data can be written to the TXB0 register.

Caution The TXBF0 and TXSF0 bits of the ASIF0 register change “10”

→

“11”

→

“01” during

continuous transmission. Therefore, do not confirm the status based on the combination

of the TXBF0 and TXSF0 bits.

Judge the status based only on the TXBF0 bit when performing continuous transmission.

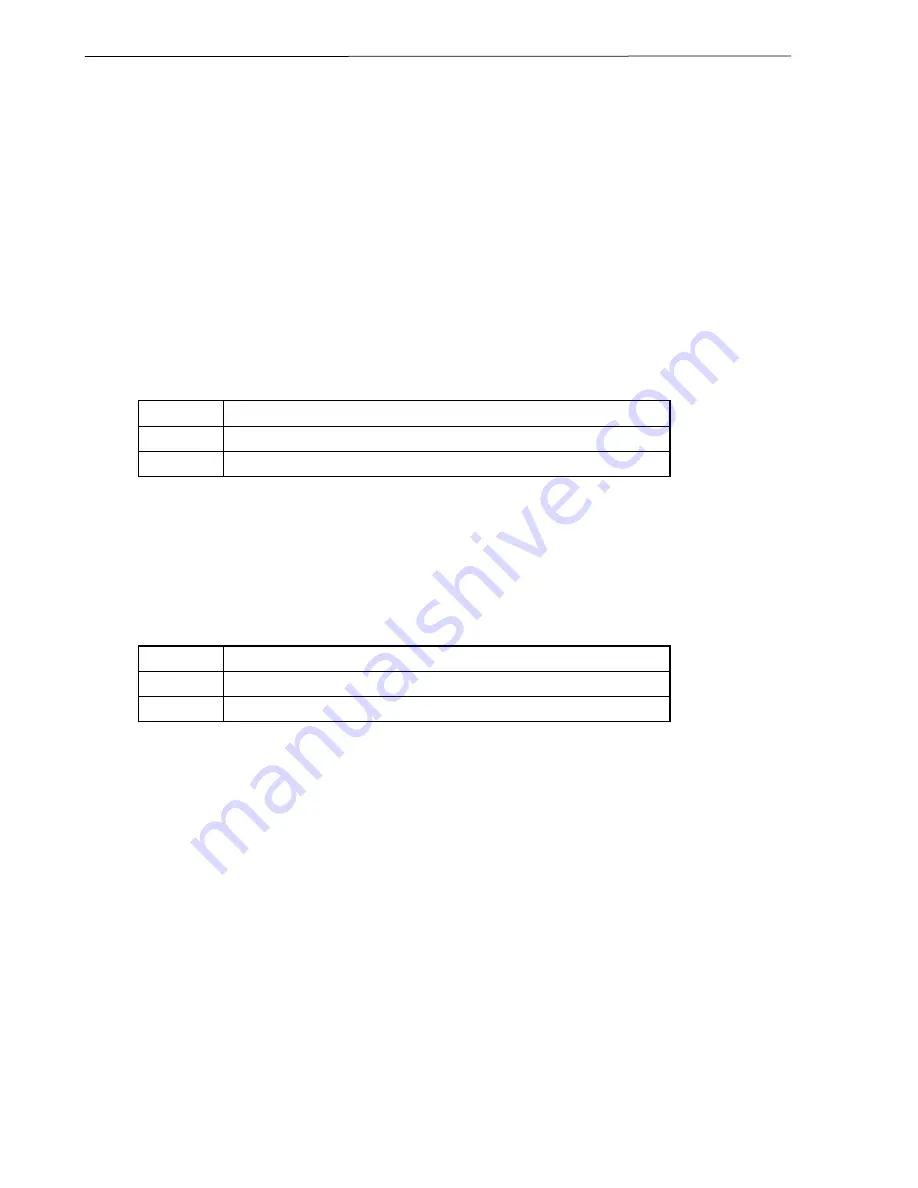

TXBF0

Whether or Not Writing to TXB0 Register Is Enabled

0

Writing is enabled

1

Writing is not enabled

Caution When transmission is performed continuously, write the first transmit data (first byte) to the

TXB0 register and confirm that the TXBF0 bit is 0, and then write the next transmit data

(second byte) to TXB0 register. If writing to the TXB0 register is performed when the TXBF0

bit is 1, transmit data cannot be guaranteed.

The communication status can be confirmed with the TXSF0 bit.

TXSF0 Transmission

Status

0

Transmission is completed.

1

Under transmission.

Cautions 1. When initializing the transmission unit when continuous transmission is completed,

confirm that the TXBF0 bit is 0 after the occurrence of the transmission completion

interrupt, and then execute initialization. If initialization is performed when the TXBF0

bit is 1, transmit data cannot be guaranteed.

2. While transmission is being performed continuously, an overrun error may occur if the

next transmission is completed before the INTST0 interrupt servicing following the

transmission of 1 data frame is executed. An overrun error can be detected by

embedding a program that can count the number of transmit data and referencing

TXSF0 bit.