ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

679

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

PD.4

MFP2

SPI1_MISO

PC.1

MFP3

PD.3

MFP2

SPI1_MOSI

PC.0

MFP3

PD.2

MFP2

SPI1_SS

PC.3

MFP3

PD.5

MFP2

SPI1_I2SMCLK

PC.4

MFP3

PD.6

MFP2

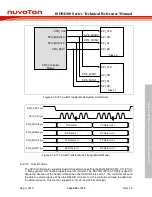

6.14.4.3 SPI2 Basic Configurations

Clock source configuration

–

Select the source of SPI0 peripheral clock on SPI2SEL (CLK_CLKSEL2[7:6]).

–

Enable SPI0 peripheral clock in SPI2CKEN (CLK_APBCLK0[14]).

Reset configuration

–

Reset SPI0 controller in SPI2RST (SYS_IPRST1[14]).

Pin configuration

Group

Pin Name

GPIO

MFP

SPI2

SPI2_CLK

PA.10

MFP4

PC.7

MFP2

SPI2_MISO

PA.7

MFP4

PC.6

MFP2

SPI2_MOSI

PA.8

MFP4

PC.5

MFP2

SPI2_SS

PA.9

MFP4

PC.8

MFP2

SPI2_I2SMCLK

PA.12

MFP4

PC.9

MFP2

SPI/I2S (SPI1~SPI2) Interface Controller Pin description is shown as follows:

Pin

SPI Mode

I

2

S Mode

SPIx_SS

SPI slave selection pin

I

2

S left/right channel synchronization clock pin (I2Sx_LRCLK)

SPIx_CLK

SPI clock pin

I

2

S bit clock pin (I2Sx_BCLK)

SPIx_MISO

SPI master input or slave output pin

I

2

S data input pin (I2Sx_DI)