ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

140

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

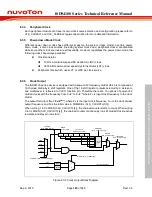

6.3 Clock Controller

6.3.1

Overview

The clock controller generates clocks for the whole chip, including system clocks and all peripheral

clocks. The clock controller also implements the power control function with the individually clock

ON/OFF control, clock source selection and a clock divider. The chip will not enter Power-down

mode until CPU sets the Power-down enable bit PDEN(CLK_PWRCTL[7]) and Cortex

®

-M4 core

executes the WFI instruction. After that, chip enters Power-down mode and wait for wake-up

interrupt source triggered to leave Power-down mode. In Power-down mode, the clock controller

turns off the 4~24.576 MHz external high speed crystal (HXT) and internal high speed RC oscillator

(HIRC) to reduce the overall system power consumption. The Figure 6.3-1 shows the clock

generator and the overview of the clock source control.