ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

45

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

5

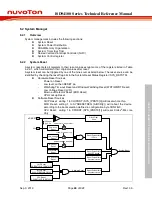

BLOCK DIAGRAM

5.1

ISD94100 Series Block Diagram

ARM

Cortex

TM

-M4

(DSP/FPU/ETM)

200MHz

APROM

512KB

SRAM 192KB

LDROM 4KB

Data Flash share

with APROM

POR / LVR / BOD

CPU core LDO

1.2V

Memory

Power control

Timer / PWM

Timer x4

WDT x1/WWDT x1

PWM x6

RTC

Analog Interface

12-bit ADC 13-ch

HS Osc.

48.0/49.152MHz

LS Osc. 10KHz

PLL 100~500MHz

HS Ext. Crystal

4~24.576MHz

Clock control

LS Ext. Crystal

32.768KHz

PDMA

16-ch

GPIO

External interrupt

General Purpose

IO

Connectivity

UART0 x1

I2C x2

(SPI/I2S) x2

SPI (Quad) x1

AHB Bus

Bridge

Security

CRC

APB Bus

USB 1.1 Device

I2S

DMIC

DPWM

Figure 5.1-1 ISD94100 Series Block Diagram