MOD E L 3562A

4. Con nect the signatu re analyzer according to table A2-2.

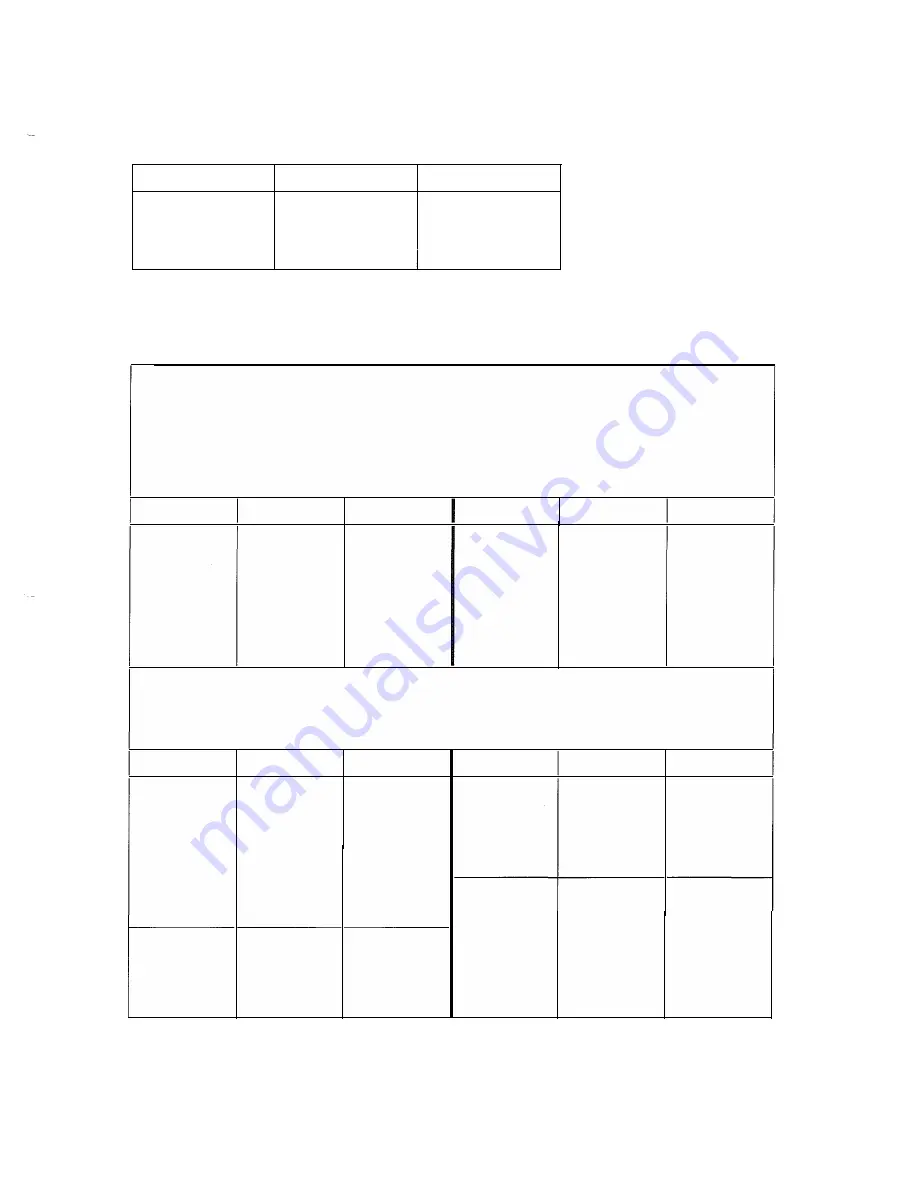

Table J�2-2 CPU Signature Analyzer Setup

Signal

Polarity

Connection

G round

A2 J 2-1

C lock

Positive edge

A2 J2-3

Stop

Negative edge

A2 J2-4

Start

Negative edge

A2 J2-5

5. Connect the power cable and press the l ine switch on.

Table A2-3 CPU Signature Analysis Test

#1

Address Test

J u m pers in test (T) pos ition: A2J4, A2J 5, A2J6, A2J 7, A2J 9, A2J 1 0, A2J 1 8

J umpers in position "2": A2J1 1 , A2J14

J umpers in normal (N) position: A2J 1 , A2J8, A2J1 7, A2J 1 2, A2J 1 3

J u m pers i n either normal o r test pos ition: A2J1 5, A2J 1 6

Signature Analyzer Setup: Refer to table A2-2

+

5 V Signature

=

0001

Component

Pin

Signature

Component

U1 00

29

U U U U

U100

30

5555

31

CCCC

32

7F7F

33

5 H21

34

OAFA

35

U PFH

36

52F8

Pin

Signature

37

HC89

38

2 H 70

39

H PPO

40

1 293

41

HAP7

42

3C96

43

3827

44

755U

Put jumper J1 in pos ition "1 ". It takes about 1 0s for each of the fol l owing s ignatures to stabi l ize.

+ 5 V Si gnature

=

6PCP

Component

Pin

Signature

Component

Pin

Signature

U1 00

45

2595

U305

1 4

0000

46

1 F8F

1 5

H U HA

47

U97F

1 6

1 582

48

5A34

1 7

AC4F

49

6PCP

1 8

01 2U

50

91 FC

51

3CPF

52

A70F

U606

1 3

443U

1 5

6PCP

U305

1 0

4CAH

1 6

AP1 8

1 1

2 H 3 U

1 7

A52A

1 2

3 H FO

1 8

UA2U

1 3

807A

SERVICE

8-33

Summary of Contents for 3562A

Page 2: ......

Page 6: ......

Page 16: ...GEN ERAL INFORMATION MODEL 3562 T bJe 1 3 Specifications cont 1 10 ...

Page 20: ......

Page 24: ......

Page 126: ......

Page 128: ......

Page 150: ......

Page 152: ......

Page 160: ......

Page 196: ......

Page 198: ......

Page 206: ......

Page 207: ...MODEL 3562A CR Cl ...

Page 209: ...MODE L 3562A Cl ...

Page 211: ... ...

Page 213: ...r A1 a pQWERSuP PLY I 03562 66518 REV A REV 8 8MPOUT 58 58 FRONT REAR P ANEL ii O N ...

Page 214: ... C401 8S1 15ISI t 1 J400 ...

Page 217: ... ...

Page 220: ......

Page 221: ... ...

Page 224: ...A3 CQVLCLI A3 ...

Page 231: ...S V InO 3J nOS N I l3 3 1 1 1X3 NI 31dWVS lX3 H l 1 3 NNVH I 0 Ioe J ...

Page 237: ...Sample Clock SAMP DS DATA oe _ _ _ _ _ BUS NOTE FULL SPA BASi BAI MODE ...

Page 246: ......

Page 259: ...WRITEL A22L l cc E Vl 8 MHz A23L ASL Inverting A1L A21 L D rivers r ...

Page 305: ...c c I O Sequencer S r J Sequence Decoder ...

Page 320: ......

Page 324: ...EXT TRIGGER TRIG 1 TRIG 2 CALTRIG CNTLD COMI W CNTCLK LDTRGL RESETL ...

Page 327: ... RH r I N EXT BUFFER SAMPLE _ _ _ IN ...

Page 450: ......

Page 488: ......

Page 492: ......

Page 536: ......

Page 552: ......

Page 570: ......