Appendix E. Processor Core Register Summary

E-27

MPC8240-Specific Registers

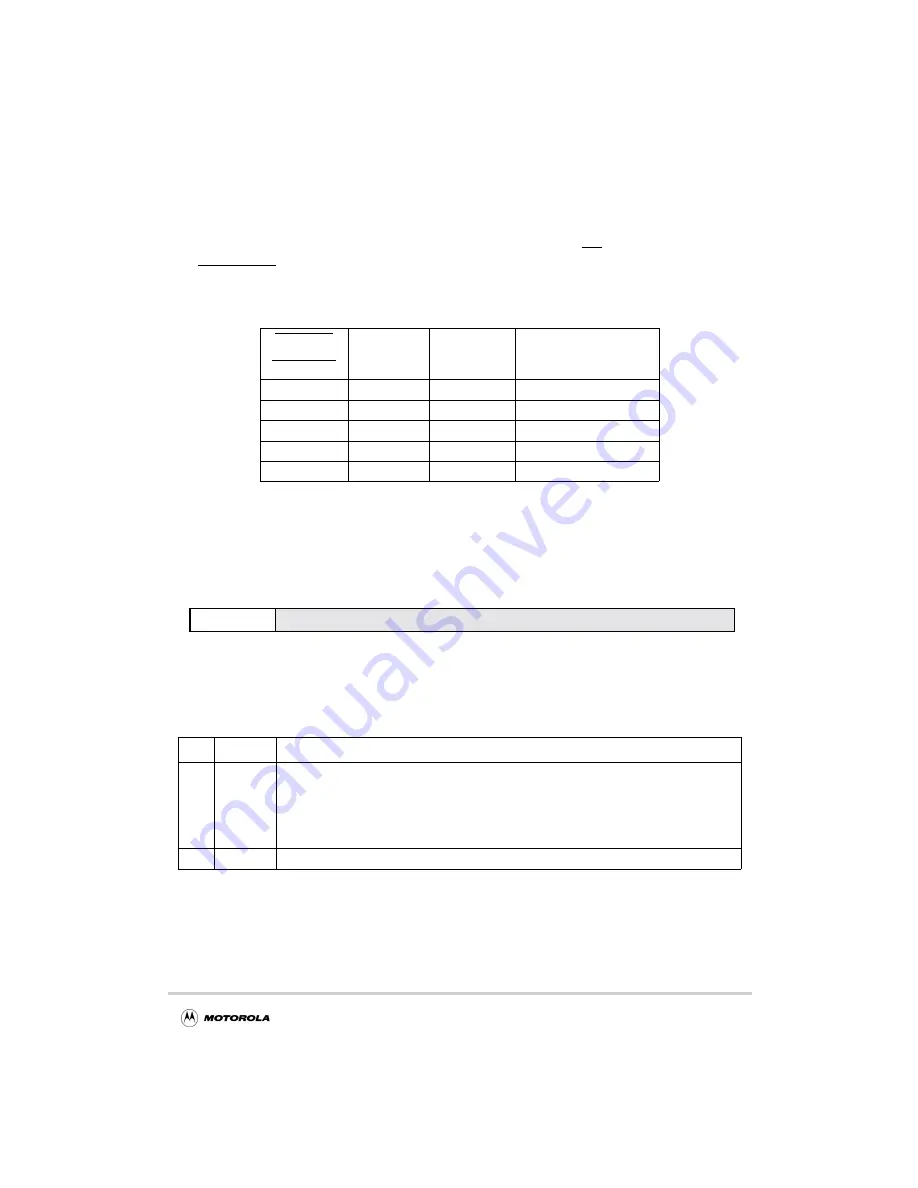

Table E-21 shows how HID0[SBCLK], HID0[ECLK], and the hard reset signals are used

to configure CKO when PMCR1[CKO_SEL] = 0. When PMCR1[CKO_SEL] = 1, the

CKO_MODE field of PMCR1 determines the signal driven on CKO. Note that the initial

value of PMCR1[CKO_SEL] is determined by the value on the AS signal at the negation

of HRST_CPU. See Section 2.2.7.8, “Debug Clock (CKO)—Output,” and Section 2.4,

“Configuration Signals Sampled at Reset,” for more information.

E.3.2 Hardware Implementation-Dependent Register 1

(HID1)

The MPC8240 implementation of HID1 is shown in Figure E-28. HID1 can be accessed

with mfspr using SPR1009.

Figure E-28. Hardware Implementation Register 1 (HID1)

Table E-22 shows the bit definitions for HID1.

Table E-21. HID0[BCLK] and HID0[ECLK] CKO Signal Configuration

HRST_CPU

and

HRST_CTRL

HID0[ECLK]

HID0[SBCLK]

Signal Driven on CKO

Asserted

x

x

sys-logic-clk

Negated

0

0

High impedance

Negated

0

1

sys-logic-clk divided by 2

Negated

1

0

Processor core clock

Negated

1

1

sys-logic-clk

Table E-22. HID1 Field Descriptions

Bits

Name

Function

0–4

PLLRATIO

PLL configuration processor core frequency ratio—This read-only field is determined by the

value on the PLL_CFG[0–4] signals during reset and the processor-to-memory clock frequency

ratio defined by that PLL_CFG[0–4] value. See MPC8240 Hardware Specification for a listing of

supported settings. Note that multiple settings of the PLL_CFG[0–4] signals can map to the

same PLLRATIO value. Thus, system software cannot read the PLLRATIO value and associate

it with a unique PLL_CFG[0–4] value.

5–31

—

Reserved

PLLRATIO

000 0000 0000 0000 0000 0000 0000

0

1

2

3

4

5

31

Содержание MPC8240

Страница 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Страница 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Страница 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Страница 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Страница 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Страница 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Страница 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Страница 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Страница 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Страница 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Страница 516: ...16 14 Watchpoint Trigger Applications ...

Страница 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Страница 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Страница 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...