E-10

MPC8240 Integrated Processor User’s Manual

PowerPC Register Set

E.1.2 PowerPC VEA Register Set—Time Base

The PowerPC virtual environment architecture (VEA) defines registers in addition to those

defined by the UISA. The PowerPC VEA register set can be accessed by all software with

either user- or supervisor-level privileges. Figure E-1 provides a graphic illustration of the

PowerPC VEA register set included in the MPC8240.

The PowerPC VEA introduces the time base facility (TB), a 64-bit structure that consists

of two 32-bit registers—time base upper (TBU) and time base lower (TBL), whose contents

are incremented once every four sys_logic_clk cycles on the MPC8240. Note that the time

base registers can be accessed by both user- and supervisor-level instructions. In the context

of the VEA, user-level applications are permitted read-only access to the TB. The OEA

defines supervisor-level access to the TB for writing values to the TB. See Section E.1.3.9,

“Time Base Facility (TB)—OEA; Writing to the Time Base,” for more information.

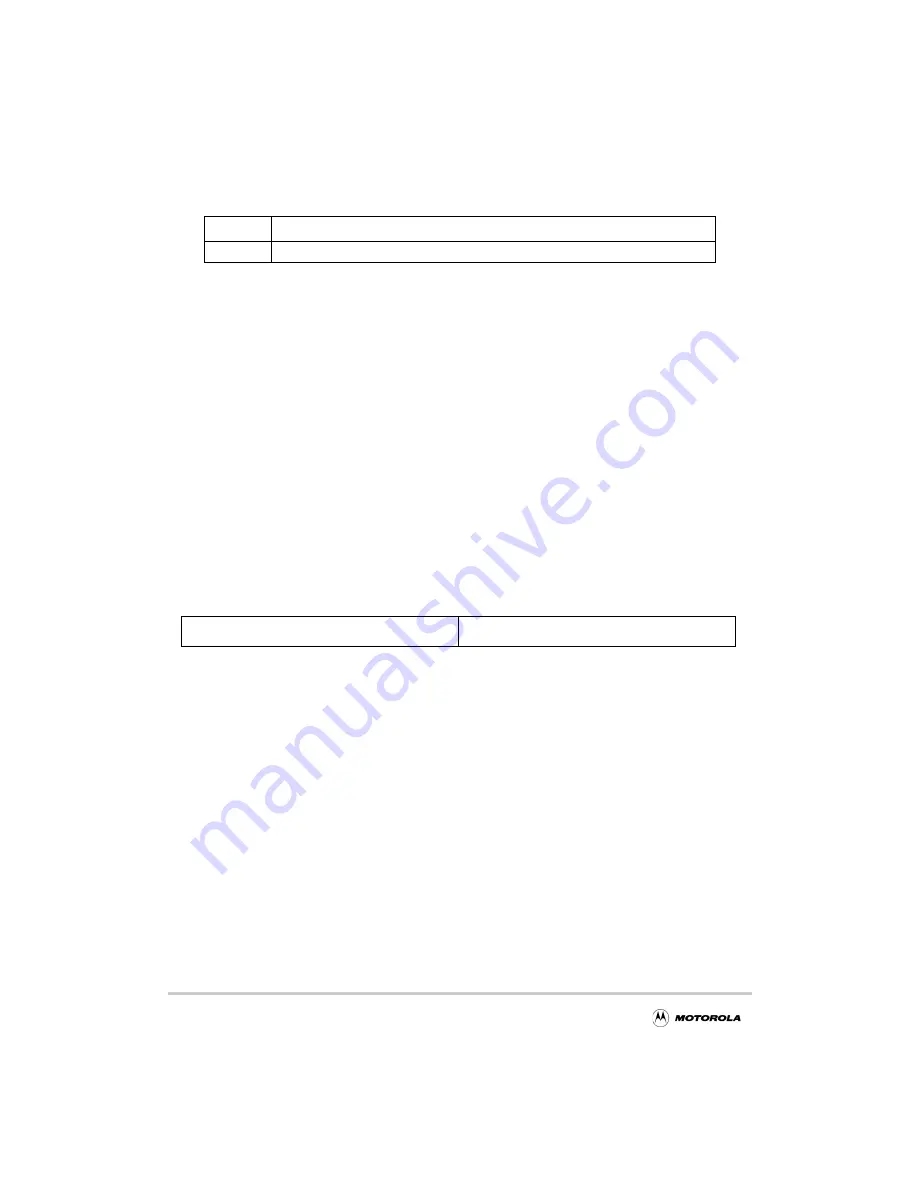

The time base (TB) is shown in Figure E-9.

Figure E-9. Time Base (TB)

E.1.2.1 Reading the Time Base

The mftb instruction is used to read the time base. For information on writing the time base,

see Section E.1.3.9, “Time Base Facility (TB)—OEA; Writing to the Time Base.”

On 32-bit implementations, it is not possible to read the entire 64-bit time base in a single

instruction. The mftb simplified mnemonic moves from the lower half of the time base

register (TBL) to a GPR, and the mftbu simplified mnemonic moves from the upper half

of the time base (TBU) to a GPR.

Because of the possibility of a carry from TBL to TBU occurring between reads of the TBL

and TBU, a sequence such as the following example is necessary to read the time base on

32-bit implementations:

loop:

mftbu

rx

#load from TBU

mftb

ry

#load from TBL

mftbu

rz

#load from TBU

cmpw

rz,rx

#see if ‘old’ = ‘new’

bne

loop

#loop if carry occurred

1z1zz

Branch always.

Notes: The y bit provides a hint about whether a conditional branch is likely to be taken and is used by

some PowerPC implementations to improve performance. Other implementations may ignore the

y bit.

The z indicates a bit that is ignored. The z bits should be cleared (zero), as they may be assigned

a meaning in a future version of the PowerPC UISA.

Table E-7. BO Operand Encodings (Continued)

BO

Description

0

31 0

31

TBU—Upper 32 bits of time base

TBL—Lower 32 bits of time base

Содержание MPC8240

Страница 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Страница 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Страница 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Страница 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Страница 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Страница 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Страница 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Страница 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Страница 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Страница 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Страница 516: ...16 14 Watchpoint Trigger Applications ...

Страница 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Страница 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Страница 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...