9-2

MPC8240 Integrated Processor User’s Manual

Message and Doorbell Register Programming Model

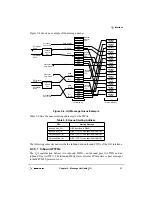

9.2 Message and Doorbell Register Programming

Model

The message and doorbell registers are described in the following subsections. Note that

the interrupt status and interrupt mask bits for the message and doorbell registers are in the

OMISR, OMIMR, IMISR, and IMIMR I

2

O registers. See Section 9.3.4.1, “PCI-Accessible

I2O Registers” and Section 9.3.4.2, “Processor-Accessible I2O Registers,” for more

information about these registers.

The outbound message and doorbell registers are used to communicate with a PCI host by

asserting the INTA signal on the PCI bus. The PCI host is defined as the device that handles

the PCI interrupts.

The message and doorbell registers can also be used to perform peer-to-peer

communication such as between multiple MPC8240 devices in a system. In this scenario,

only the inbound registers need to be used and should be all mapped to different PCSRBAR

locations. Because there is not a host in this scenario, INTA is not generated (and the

outbound registers are not used).

9.2.1 Message and Doorbell Register Summary

MPC8240 contains two 32-bit inbound message registers (IMR0 and IMR1) and two 32-bit

outbound message registers (OMR0 and OMR1) that function in both host and agent mode.

Table 9-1 summarizes the message registers.

The MPC8240 also contains a 32-bit inbound and a 32-bit outbound doorbell register

(IDBR and ODBR, respectively). Table 9-2 summarizes the doorbell registers.

Table 9-1. Message Register Summary

PCI Offset

Local Memory

Offset

Acronym

Name

0x050

0x0_0050

IMR0

Inbound message register 0

0x054

0x0_0054

IMR1

Inbound message register 1

0x058

0x0_0058

OMR0

Outbound message register 0

0x05C

0x0_005C

OMR1

Outbound message register 1

Table 9-2. Doorbell Register Summary

PCI Offset

Local Memory

Offset

Acronym

Name

0x060

0x0_0060

ODBR

Outbound doorbell register

0x068

0x0_0068

IDBR

Inbound doorbell register

Содержание MPC8240

Страница 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Страница 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Страница 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Страница 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Страница 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Страница 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Страница 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Страница 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Страница 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Страница 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Страница 516: ...16 14 Watchpoint Trigger Applications ...

Страница 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Страница 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Страница 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...