Chapter 8. DMA Controller

8-23

DMA Register Descriptions

8.7.8 Next Descriptor Address Registers (NDARs)

The NDARs contain the address for the next descriptor in memory. Software is not expected

to initialize this register. This register contains valid information only after the DMA engine

has fetched a descriptor that was pointed to by the CDAR. All data bits, with the exception

of EOTD, belong to the next descriptor to be loaded and executed. When the data bits are

transferred to the CDAR, the bits become effective for the current transfer.

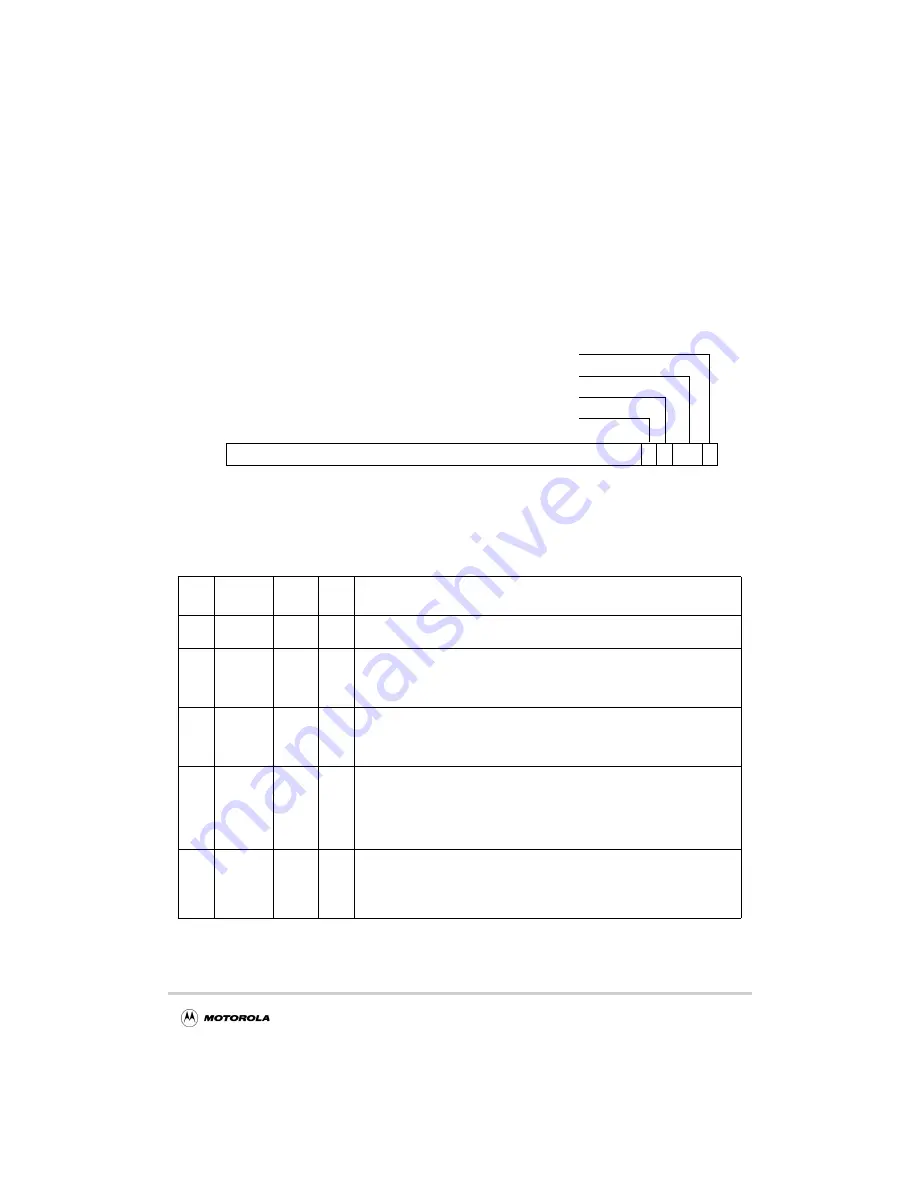

Figure 8-10 shows the bits in the NDARs.

Figure 8-10. Next Descriptor Address Register (NDAR)

Table 8-4 describes the bit settings for the NDARs.

Table 8-9. NDAR Field Descriptions—Offsets 0x124, 0x224

Bits

Name

Reset

Value

R/W

Description

31–5

NDA

All 0s

RW

Next descriptor address. Contains the next descriptor address of the buffer

descriptor in memory; must be aligned on an 8-word boundary.

4

NDSNEN

0

RW

Next descriptor snoop enable. This bit is valid for both chaining and direct

modes.

0 Disables snooping

1 Enables processor core snooping for DMA transactions.

3

NDEOSIE

0

RW

Next descriptor end-of-segment interrupt enable. Interrupt mechanism used

depends on the setting of DMR[IRQS]. This bit is valid only for chaining mode.

0 End-of-segment interrupt disabled

1 Generates an interrupt if the DMA transfer for the next descriptor is finished.

2–1

NDCTT

00

RW

Next descriptor channel transfer type. These two bits specify the type/direction

of the DMA transfer. These bits are valid for both chaining and direct modes.

00 Local memory to local memory transfer

01 Local memory to PCI transfer

10 PCI to local memory transfer

11 PCI to PCI transfer

0

EOTD

0

RW

End-of-transfer descriptor. This bit is ignored in direct mode.

0 This descriptor is not the last descriptor in memory.

1 Indicates that this descriptor is the last descriptor in memory. If this bit is set,

NDAR bits 4, 3, 2, and 1 are ignored and the DMA controller finishes after the

current buffer transaction is finished.

NDA

31

5

4

3

2

1

0

NDSNEN

NDEOSIE

NDCTT

EOTD

Содержание MPC8240

Страница 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Страница 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Страница 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Страница 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Страница 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Страница 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Страница 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Страница 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Страница 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Страница 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Страница 516: ...16 14 Watchpoint Trigger Applications ...

Страница 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Страница 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Страница 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...