10-2

MPC8240 Integrated Processor User’s Manual

I

2

C Interface Overview

•

Bus-busy detection

•

Programmable on-chip digital filter rejecting electrical spikes on the bus

•

Module reset through software

10.1.2 I

2

C Interface Signal Summary

The I

2

C interface uses the serial data (SDA) signal and serial clock (SCL) signal for data

transfer. All devices connected to these two signals must have open-drain or open-collector

outputs. A logical AND function is performed on both signals with external pull-up

resistors. Note that the signal patterns driven on SDA represent address, data, or read/write

information at different stages of the protocol.

Table 10-1 summarizes the two signals that comprise the I

2

C interface.

10.1.3 I

2

C Register Summary

There are five registers in the I

2

C unit that are used for the address, data, configuration,

control, and status of the I

2

C interface. These registers are located in the embedded utilities

memory block; see Section 3.4, “Embedded Utilities Memory Block (EUMB).” Table 10-2

summarizes the I

2

C registers. Complete descriptions of these registers are provided in

Section 10.3, “I2C Register Descriptions.”

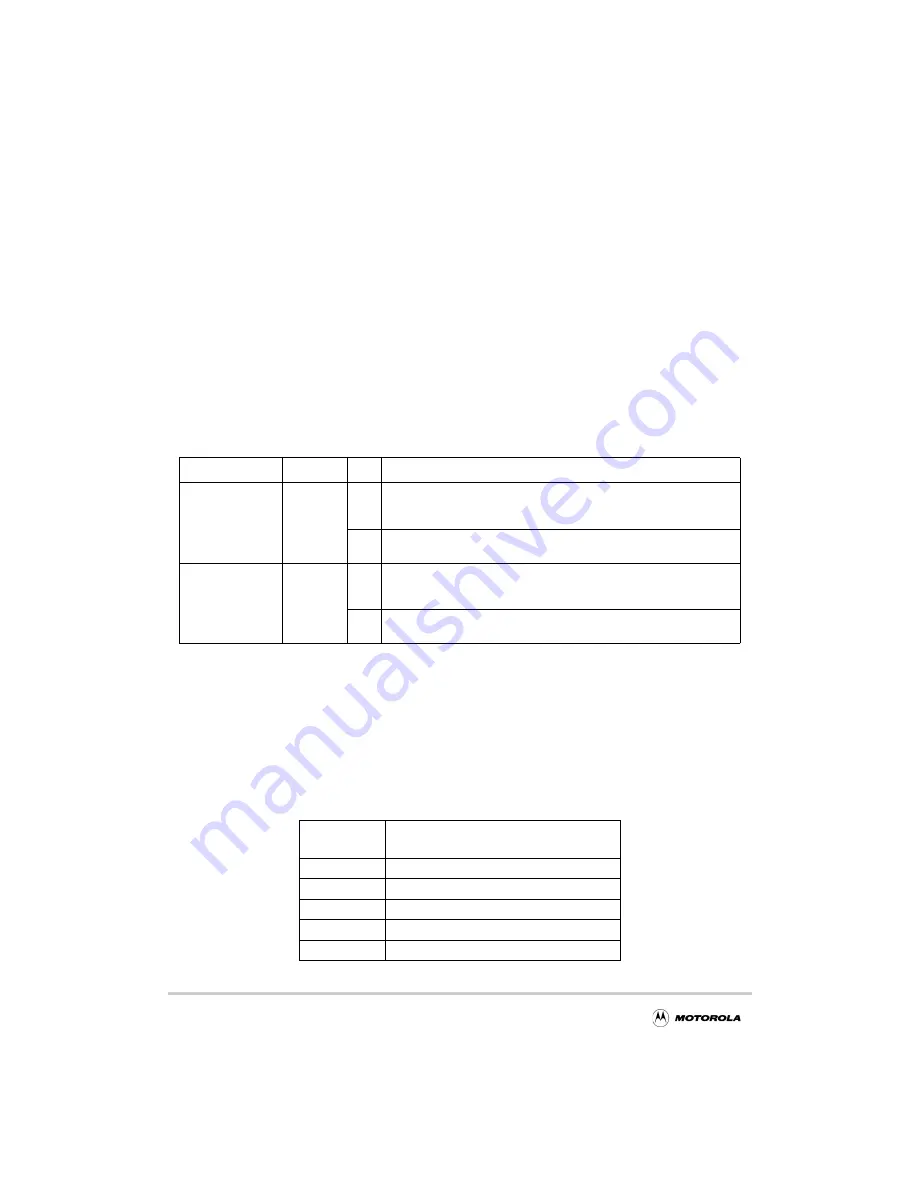

Table 10-1. I

2

C Interface Signal Description

Signal Name

Idle State

I/O

State Meaning

SCL (serial clock)

HIGH

I

When the MPC8240 is idle or acts as a slave, SCL defaults as an input.

The unit uses SCL to synchronize incoming data on SDA. The bus is

assumed to be busy when SCL is detected low.

O

As a master, the MPC8240 drives SCL along with SDA when transmitting.

As a slave, the MPC8240 drives SCL low for data pacing.

SDA (serial data)

HIGH

I

When the MPC8240 is idle or in a receiving mode, SDA defaults as an

input. The unit receives data from other

I

2

C

devices on SDA. The bus is

assumed to be busy when SDA is detected low.

O

When writing as a master or slave, the MPC8240 drives data on SDA

synchronous to SCL.

Table 10-2. I

2

C Register Summary

Local Memory

Offset

Register Name

0x0_3000

I

2

C address register (I2CADR)

0x0_3004

I

2

C frequency divider register (I2CFDR)

0x0_3008

I

2

C control register (I2CCR)

0x0_300C

I

2

C status register (I2CSR)

0x0_3010

I

2

C data register (I2CDR)

Содержание MPC8240

Страница 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Страница 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Страница 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Страница 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Страница 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Страница 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Страница 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Страница 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Страница 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Страница 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Страница 516: ...16 14 Watchpoint Trigger Applications ...

Страница 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Страница 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Страница 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...