Appendix E. Processor Core Register Summary

E-21

Implementation-Specific Registers from 603e

E.2.1 Data and Instruction TLB Miss Address Registers

(DMISS and IMISS)

The DMISS and IMISS registers have the same format as shown in Figure E-22. They are

loaded automatically upon a data or instruction TLB miss. The DMISS and IMISS contain

the effective page address of the access that caused the TLB miss exception. The contents

are used by the 603e when calculating the values of HASH1 and HASH2, and by the tlbld

and tlbli instructions when loading a new TLB entry. Note that the 603e always loads the

DMISS register with a big-endian address, even when MSR[LE] is set. These registers can

be read and written by software.

Figure E-22. DMISS and IMISS Registers

E.2.2 Data and Instruction TLB Compare Registers

(DCMP and ICMP)

The DCMP and ICMP registers are shown in Figure E-23. These registers contain the first

word in the required PTE. The contents are constructed automatically from the contents of

the segment registers and the effective address (DMISS or IMISS) when a TLB miss

exception occurs. Each PTE read from the tables during the table search process should be

compared with this value to determine whether or not the PTE is a match. Upon execution

of a tlbld or tlbli instruction the upper 25 bits of the DCMP or ICMP register and 11 bits

of the effective address operand are loaded into the first word of the selected TLB entry.

These registers can be read and written by software.

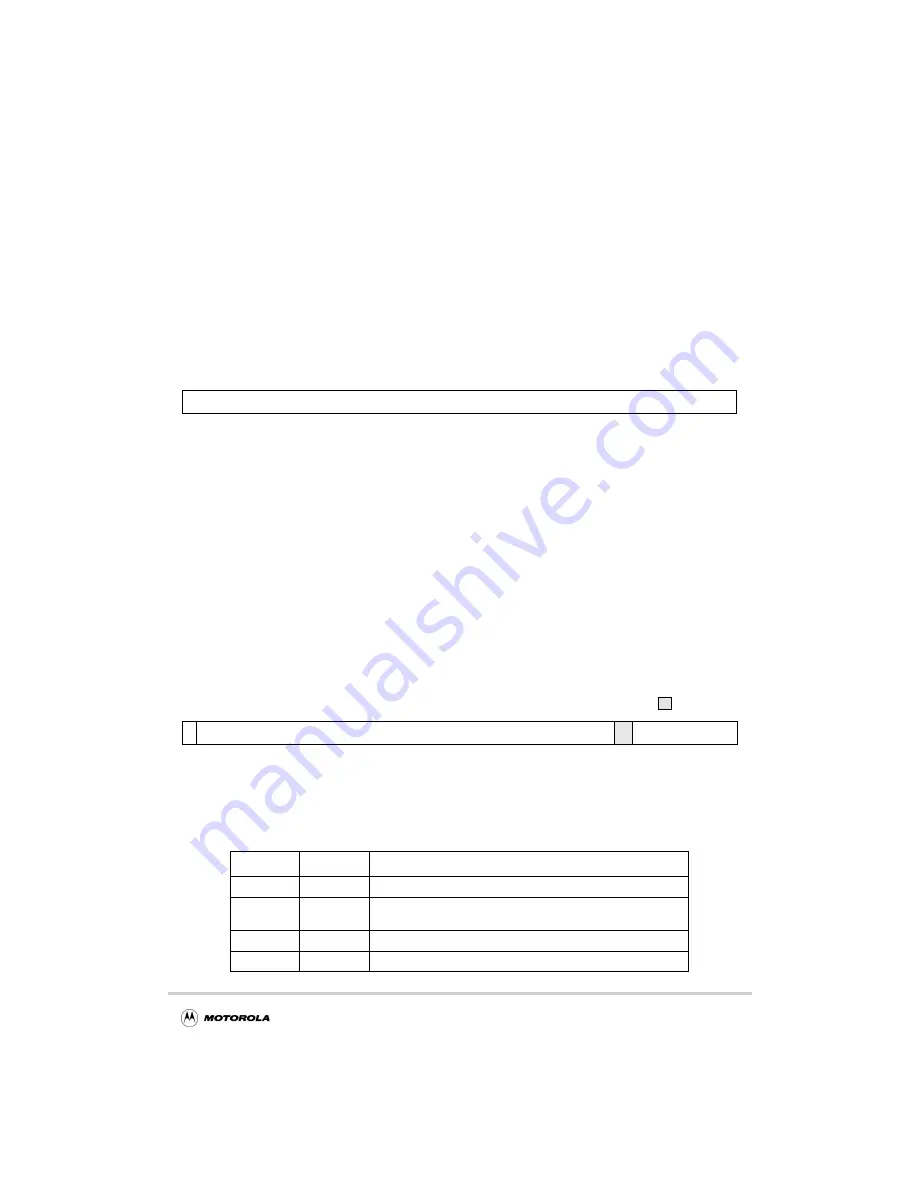

Figure E-23. DCMP and ICMP Registers

Table E-16 describes the bit settings for the DCMP and ICMP registers.

Table E-16. DCMP and ICMP Bit Settings

Bits

Name Description

0

V

Valid bit. Set by the processor on a TLB miss exception.

1–24

VSID

Virtual segment ID. Copied from VSID field of corresponding

segment register.

25

—

Reserved

26–31

API

Abbreviated page index. Copied from API of effective address.

0

31

Effective Page Address

0 1

24 25 26

31

V

VSID

API

0

Reserved

Содержание MPC8240

Страница 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Страница 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Страница 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Страница 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Страница 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Страница 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Страница 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Страница 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Страница 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Страница 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Страница 516: ...16 14 Watchpoint Trigger Applications ...

Страница 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Страница 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Страница 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...