Chapter 2. Signal Descriptions and Clocking

2-19

Detailed Signal Descriptions

State Meaning

Asserted/Negated—Selects the SDRAM internal bank to be

activated during the row address phase and selects the SDRAM

internal bank for the read or write operation during the column

address phase of the memory access. See Section 6.2.2, “SDRAM

Address Multiplexing,” for a complete description of the mapping of

these signals in all cases.

Timing Comments

Assertion/Negation—The row address is valid on the rising edge of

SDRAM_CLK[0:3] clock signals when CSn is asserted and the

column address is valid on the rising edge of SDRAM_CLK[0:3]

when DQMn is asserted.

2.2.2.9 Memory Data Bus (MDH[0:31], MDL[0:31])

The memory data bus (MDH[0:31], MDL[0:31]) consists of 64 signals that are both input

and output signals on the MPC8240. The data bus is comprised of two halves—data bus

high (MDH[0:31]) and data bus low (MDL[0:31]).

The MPC8240 can also be configured to operate with a 32-bit data bus on the memory

interface by driving the reset configuration signal MDL0 low during reset. When the

MPC8240 is configured with a 32-bit data bus, the bus operates in the same way as when

configured with a 64-bit data bus, with the exception that only MDH[0:31] is used, and

MDL[0:31] can be left floating. For more information on other data bus sizes available for

the ROM/Flash/Port X interfaces, see Chapter 6, “MPC8240 Memory Interface.”

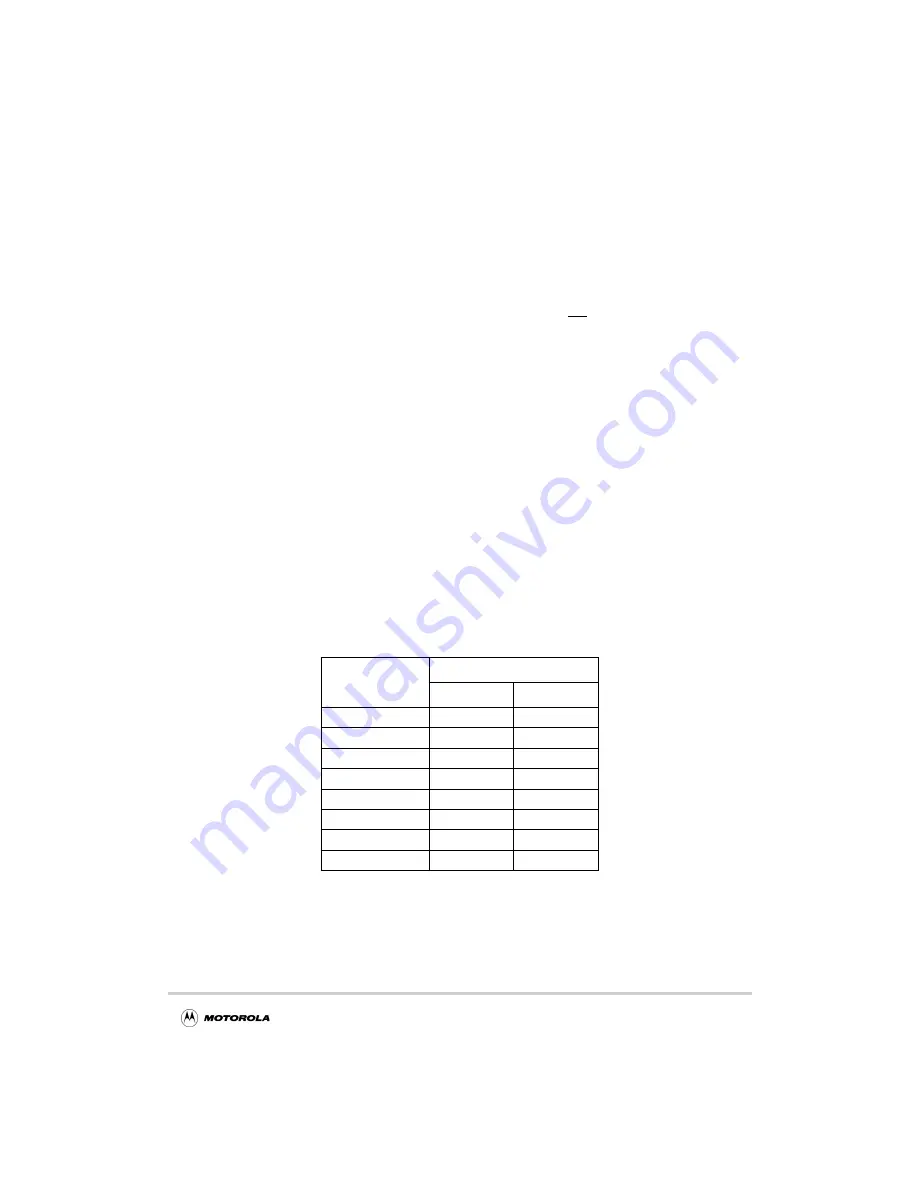

Table 2-4 specifies the byte lane assignments (and data parity signal correspondence) for

the transfer of an aligned double word in both 64- and 32-bit modes.

Table 2-4. Memory Data Bus Byte Lane Assignments

Data Bus Signals

Byte Lane

64-Bit Mode

32-Bit Mode

MDH[0:7]

0 (MSB)

0 (MSB), 4

MDH[8:15]

1

1, 5

MDH[16:23]

2

2, 6

MDH[24:31]

3

3, 7 (LSB)

MDL[0:7]

4

x

MDL[8:15]

5

x

MDL[16:23]

6

x

MDL[24:31]

7 (LSB)

x

Содержание MPC8240

Страница 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Страница 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Страница 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Страница 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Страница 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Страница 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Страница 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Страница 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Страница 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Страница 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Страница 516: ...16 14 Watchpoint Trigger Applications ...

Страница 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Страница 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Страница 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...