8-16

MPC8240 Integrated Processor User’s Manual

DMA Register Descriptions

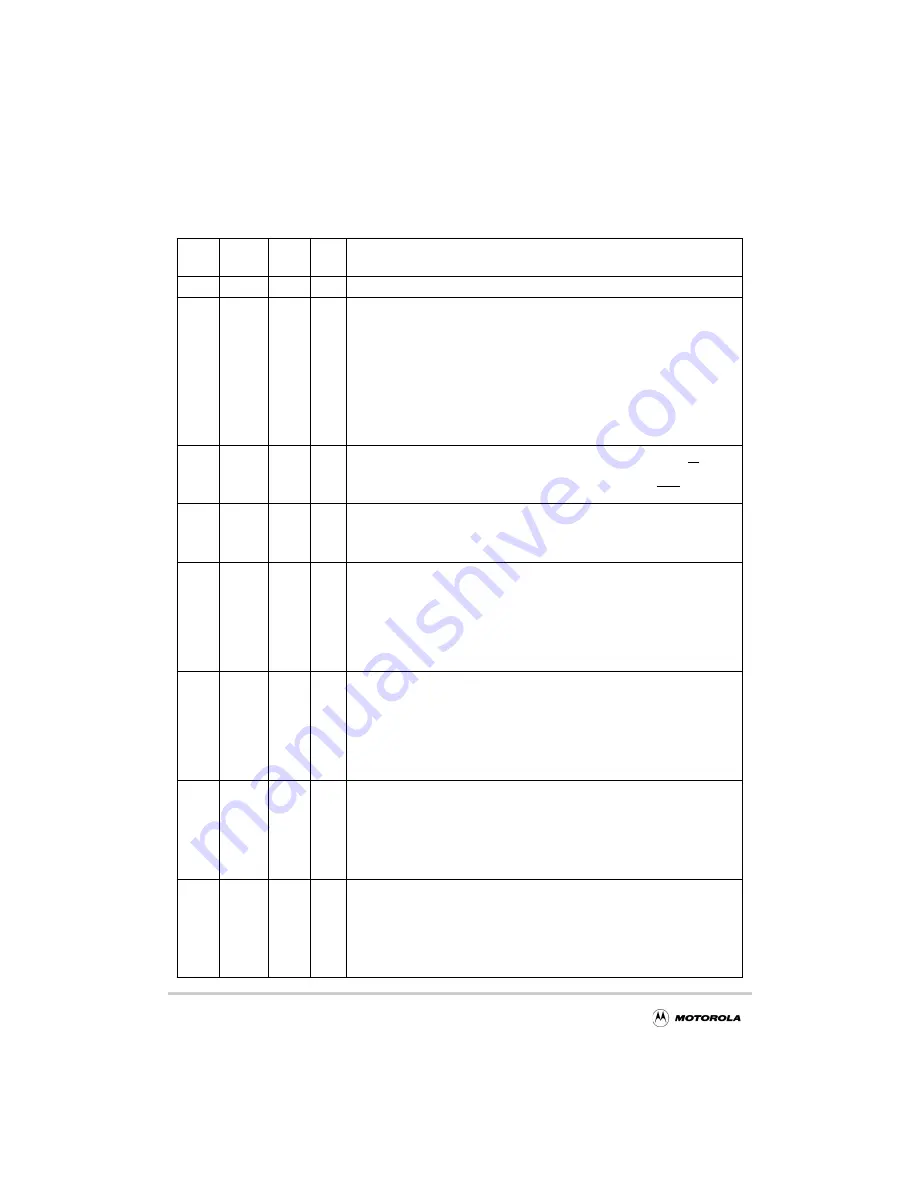

Table 8-3 describes the bit settings for the DMRs.

Table 8-3. DMR Field Descriptions—Offsets 0x100, 0x200

Bits

Name

Reset

Value

R/W

Description

31–22

—

0

R

Reserved

21–20

LMDC

00

RW

Local memory delay count. This field controls the delay between the DMA transfer

of each cache line (32 bytes) access to local memory. The delay value is the time

from the last successful DMA transfer until the next request occurs to local

memory. Increasing this value to something greater than 0b00 gives a greater

probability of PCI accesses gaining arbitration to the shared processor/memory

bus while a DMA transfer is in progress. Refer to Section 12.2.1, “Arbitration

Between PCI and DMA Accesses to Local Memory,” for more information.

00 4 sys_logic_clk cycles

01 8 sys_logic_clk cycles

10 16 sys_logic_clk cycles

11 32 sys_logic_clk cycles

19

IRQS

0

RW

Interrupt steer

0 Routes all DMA interrupts to the processor core through the internal int

mechanism and the EPIC unit.

1 Routes all DMA interrupts to the PCI bus through the external INTA signal.

18

PDE

0

RW

Periodic DMA enable. Applies only to chaining mode. Otherwise, it is ignored.

Refer to Section 8.3.2.2, “Periodic DMA Feature,” for more information.

0 Disables periodic DMA restart

1 Allows hardware to periodically restart the DMA process.

17–16

DAHTS

00

RW

Destination address hold transfer size. Applies only to direct mode (not used in

chaining mode). Indicates the transfer size used for each transaction when the

DAHE bit is set. The BCR value must be in multiples of this size and the DAR

value must be aligned based on this size.

00 1 byte

01 2 bytes

10 4 bytes

11 8 bytes

15–14

SAHTS

00

RW

Source address hold transfer size. Applies only to direct mode (not used in

chaining mode). Indicates the transfer size used for each transaction when the

SAHE bit is set.The BCR value must be in multiples of this size and the SAR

value must be aligned based on this size.

00 1 byte

01 2 bytes

10 4 bytes

11 8 bytes

13

DAHE

0

RW

Destination address hold enable (direct mode only). Applies only to direct mode

(not used in chaining mode). Allows the DMA controller to hold the destination

address to a fixed value for every transfer. The size used for the transfers is

indicated by DAHTS. The MPC8240 only supports aligned transfers for this

feature. Only one of DAHE or SAHE may be set at one time.

0 Disables the destination address hold feature

1 Enables the destination address hold feature

12

SAHE

0

RW

Source address hold enable (direct mode only). Applies only to direct mode (not

used in chaining mode). Allows the DMA controller to hold the source address to

a fixed value for every transfer. The size used for the transfers is indicated by

SAHTS. The MPC8240 only supports aligned transfers for this feature. Only one

of DAHE or SAHE may be set at one time.

0 Disables the source address hold feature

1 Enables the source address hold feature

Содержание MPC8240

Страница 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Страница 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Страница 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Страница 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Страница 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Страница 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Страница 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Страница 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Страница 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Страница 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Страница 516: ...16 14 Watchpoint Trigger Applications ...

Страница 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Страница 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Страница 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...