11-2

MPC8240 Integrated Processor User’s Manual

EPIC Unit Overview

11.1.1 EPIC Features Summary

The EPIC unit of the MPC8240 implements the following features:

•

OpenPIC programming model

•

Support for five external interrupt sources or one serial-style interrupt (16 interrupt

sources)

•

Four global, cascadable, high-resolution timers that can be interrupt sources

•

Interrupt control for the MPC8240 I

2

C unit, DMA unit (2 channels), and message

unit (MU)

•

Support for connection of external interrupt controller device such as an 8259

Programmable Interrupt Controller (PIC)

•

In 8259 (pass-through) mode, it generates local (internal) interrupts output signal,

L_INT.

•

Processor initialization control—The processor can reset itself by setting the

processor initialization register, causing the assertion of the internal sreset signal as

described in Section 11.9.5, “Processor Initialization Register (PI).”

•

Programmable resetting of the EPIC unit through the global configuration register

•

16 programmable interrupt priority levels

•

Fully-nested interrupt delivery

•

Spurious vector generation

•

32-bit configuration registers that are aligned on 128-bit boundaries

11.1.2 EPIC Interface Signal Description

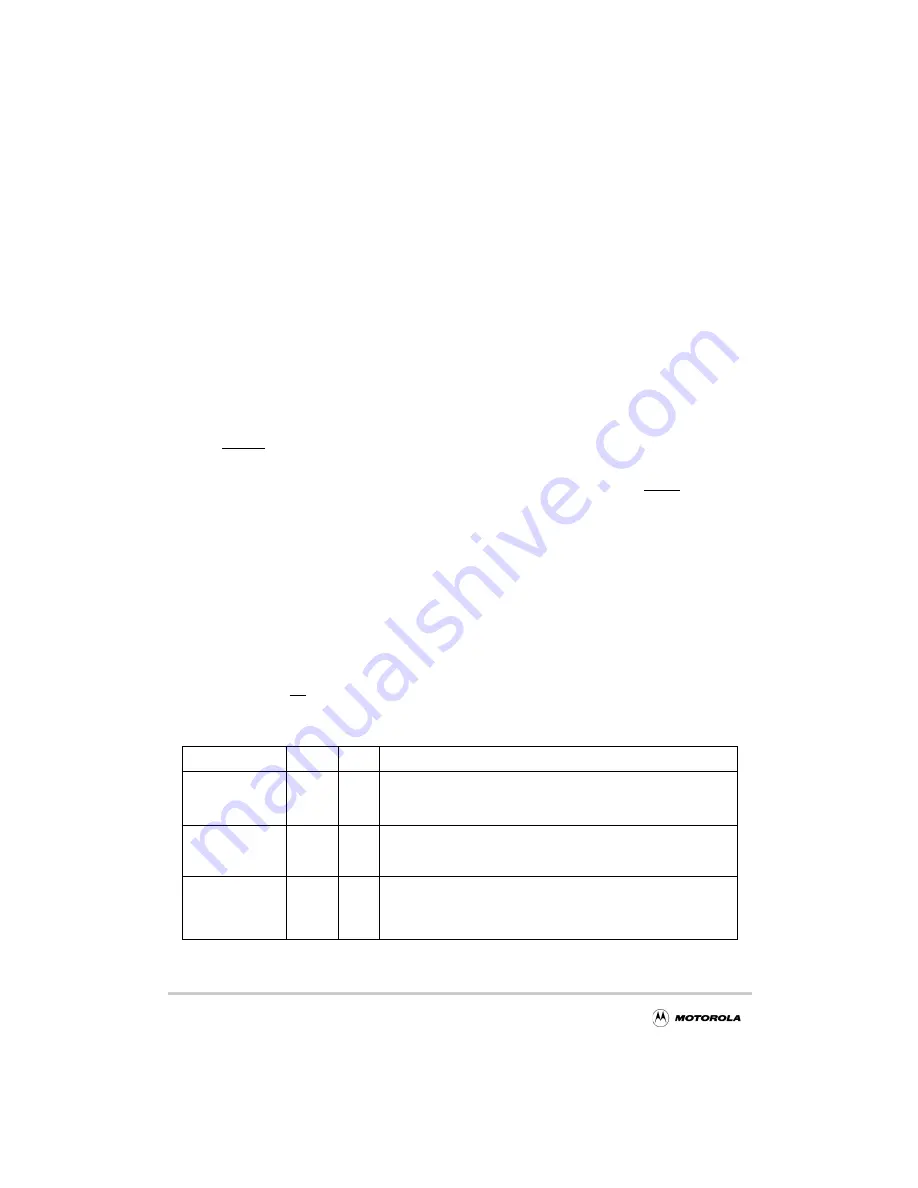

In addition to the int signal, the external EPIC signals are defined in Table 11-1.

Table 11-1. EPIC Interface Signal Description

Signal Name

Pins

I/O

State Meaning

IRQ0/S_INT

1

I

Direct IRQ mode—Input representing an incoming interrupt request.

Serial IRQ mode—Input representing the serial interrupt data stream.

Note that the IRQ0 is used when operating in the pass-through mode.

IRQ1/S_CLK

1

I/O

Direct IRQ mode—Input representing an incoming interrupt request

Serial IRQ mode—Output representing the serial clock by which the

remote sequencer (interrupt source) clocks serial interrupts out.

IRQ2/S_RST

1

I/O

Direct IRQ mode—Input representing an incoming interrupt request

Serial IRQ mode—Output pulse is active after EPIC resets and is set to

serial mode. It determines the serial interrupt slot count for all external

serial devices. Refer to Figure 11.7.

Содержание MPC8240

Страница 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Страница 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Страница 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Страница 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Страница 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Страница 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Страница 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Страница 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Страница 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Страница 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Страница 516: ...16 14 Watchpoint Trigger Applications ...

Страница 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Страница 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Страница 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...