3-16

MPC8240 Integrated Processor User’s Manual

Address Translation

The lower-order address bits of the base address field of ITWR that are within the range

specified by the window size are ignored and the MPC8240 ignores the incoming

lower-order address bits (within the range specified by the window size). However, for

future compatibility, it is recommended that the base address be programmed to be

naturally aligned to the window size. For example, if the window size is programmed as 1

Mbyte, then the base address should be aligned to a 1-Mbyte boundary (as ITWR[19–12]

are not used to determine if there is a hit to the inbound translation window for a 1-Mbyte

window).

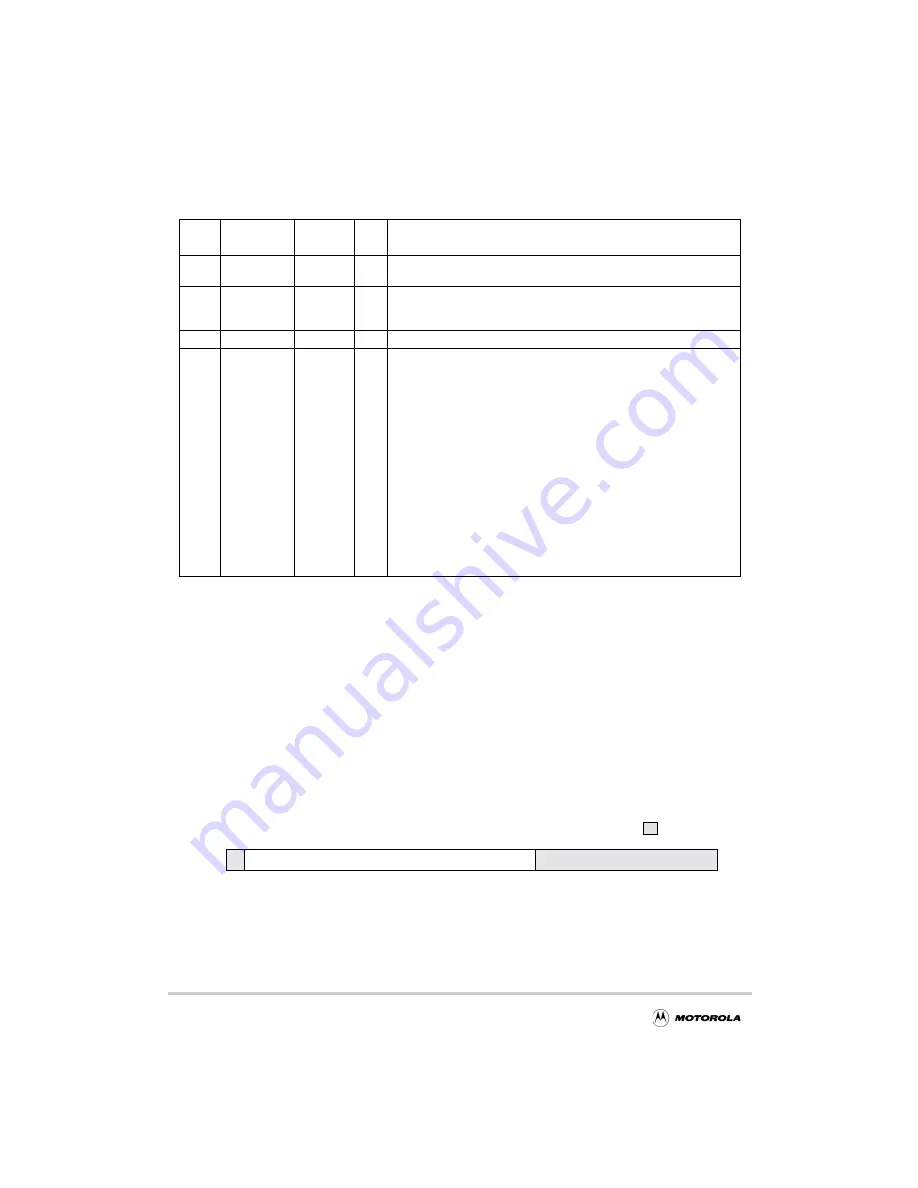

3.3.3.3 Outbound Memory Base Address Register (OMBAR)

The OMBAR, shown in Figure 3-10 and Table 3-10, defines the outbound memory

window.

Figure 3-10. Outbound Memory Base Address Register (OMBAR)—0x0_2300

Table 3-9. Bit Settings for ITWR—0x0_2310

Bits

Name

Reset

Value

R/W

Description

31

—

0

R

Reserved. Translated addresses can only be targeted at local memory in

the lower 2 Gbytes of the MPC8240 address space.

30–12 Inbound

translation

base address

Undefined

R/W

Local memory address that is the starting address for the inbound

translation window. The inbound translation window should be aligned

based on the granularity specified by the inbound window size.

11–5

—

All 0s

R

Reserved

4–0

Inbound

window size

All 0s

R/W

Inbound window size. The inbound window size is encoded as N where

the window size is 2

N+1

bytes. The minimum window size is 4 Kbytes; the

maximum window size is 1 Gbyte. Note that the inbound window size

sets the size of both the inbound memory window and the inbound

translation window.

00000 Inbound address translation disabled

00001 Reserved

...

01010 Reserved

01011 2

12

= 4 Kbyte window size

01100 2

13

= 8 Kbyte window size

01101 2

14

= 16 Kbyte window size

...

11101 2

30

= 1 Gbyte window size

11110 Reserved

11111 Reserved

Note that the inbound memory window must not overlap with the EUMB.

1

Outbound Memory Base Address

0 0 0 0 0 0 0 0 0 0 0 0

31

30

12 11

5

4

0

Reserved

Содержание MPC8240

Страница 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Страница 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Страница 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Страница 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Страница 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Страница 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Страница 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Страница 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Страница 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Страница 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Страница 516: ...16 14 Watchpoint Trigger Applications ...

Страница 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Страница 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Страница 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...