Chapter 3. Address Maps

3-1

Chapter 3

Address Maps

The MPC8240 in PCI host mode supports two address mapping configurations designated

as address map A, and address map B. The address map is selected at reset by the MAA0

configuration pin. The address map selected at reset is stored as the initial value of the

PICR1[ADDRESS_MAP] bit. If the MPC8240 is configured as a PCI host and the address

map configuration pin is pulled low, the MPC8240 uses address map A. If the MPC8240 is

configured as a PCI host and the address map configuration pin is pulled high, the

MPC8240 uses address map B.

If the MPC8240 is configured as a PCI agent, it must be configured to use address map B.

In agent mode, the MPC8240 offers address translation capability to allow address

remapping for inbound and outbound PCI memory transactions. Translation allows a

certain address space to map to a window of physical memory.

The MAA1 reset configuration pin selects whether the MPC8240 is operating as a PCI host

or agent. For more information on the reset configuration signals, see Section 2.4,

“Configuration Signals Sampled at Reset.”

Address map A conforms to the now-obsolete PowerPC reference platform (PReP)

specification. It is strongly recommended that new designs use map B because map A may

not be supported in future devices. For this reason, address map A is not described in this

chapter; instead, it is described in Appendix A, “Address Map A.”

Address map B conforms to the PowerPC microprocessor common hardware reference

platform (CHRP). When the MPC8240 is configured as a PCI agent, only map B is

supported. This chapter describes map B.

The MPC8240 also has a block of local memory and PCI memory space that is allocated to

the control and status registers for several embedded features. This block is called the

embedded utilities memory block (EUMB). The EUMB and its offsets are also described

in this chapter.

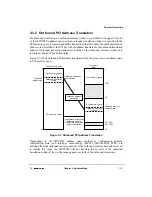

3.1 Address Map B

The address space of map B is divided into four areas—local memory, PCI memory, PCI

I/O, and system ROM space. Throughout this chapter, the term local memory is used to

mean that (S)DRAM is directly controlled by the MPC8240 memory controller.

Содержание MPC8240

Страница 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Страница 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Страница 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Страница 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Страница 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Страница 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Страница 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Страница 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Страница 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Страница 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Страница 516: ...16 14 Watchpoint Trigger Applications ...

Страница 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Страница 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Страница 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...