4-20

MPC8240 Integrated Processor User’s Manual

Output/Clock Driver and Miscellaneous I/O Control Registers

4.4 Output/Clock Driver and Miscellaneous I/O

Control Registers

Table 4-17 describes the general output driver control available with the MPC8240 through

the output driver control register (ODCR), and Table

enable/disable capability available for the clock signals through the clock driver control

register (CDCR).

Output driver control allows for impedance matching of electrical signals. When driving a

capacitive load and the polarity of the driving signal is reversed, the maximum current

driven by the output driver of a pin occurs during the transition of the signal. The output

driver strength must be configured to match the load impedance. The matched impedance

limits the maximum current driven during signal transitions. The transition current and

mismatched impedance cause ringing on the signal. If the driver level is set too strong, the

ringing intensifies. For more information on the output driver type for each signal, refer to

the MPC8240 Hardware Specification.

.

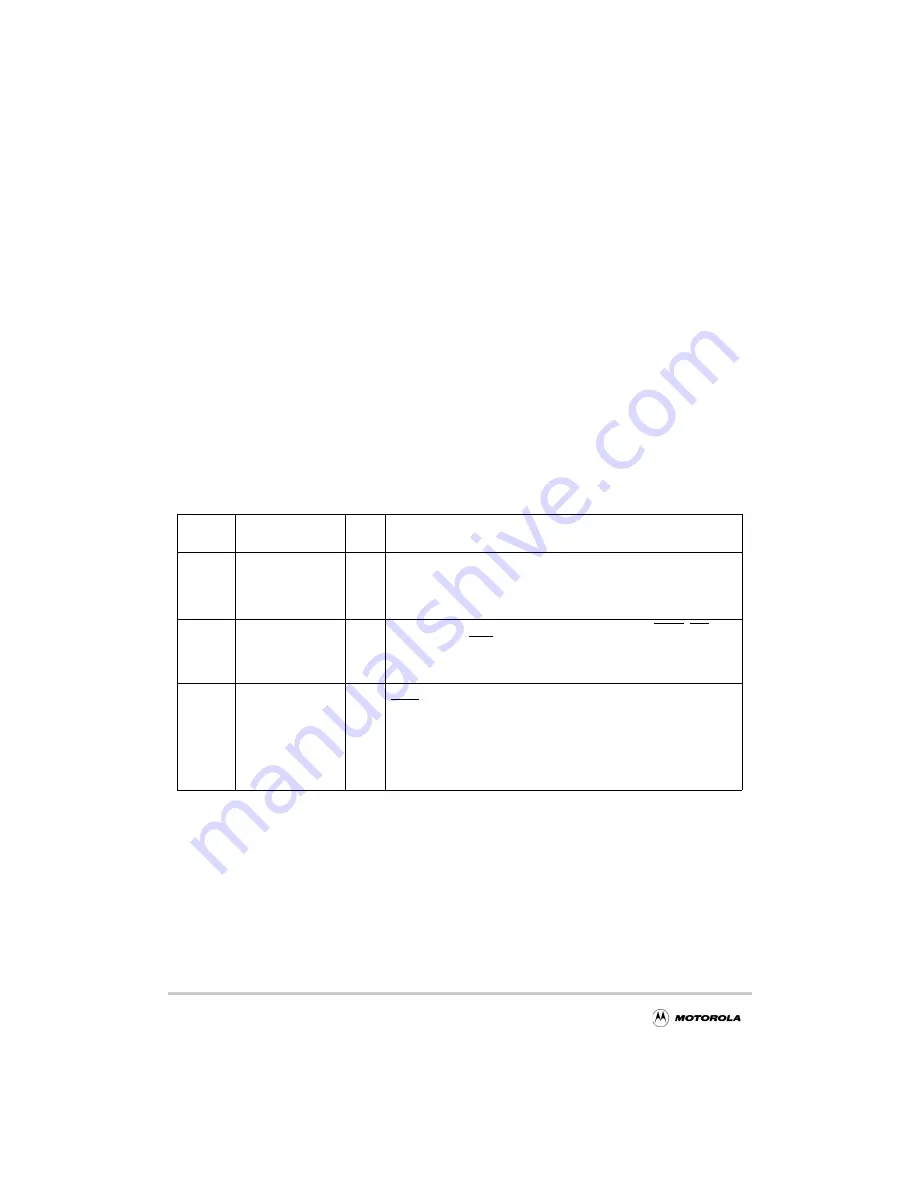

Table 4-17. Output Driver Control Register Bit Definitions—0x73

Bits Name

Reset

Value

Description

msb 7

addr<73>

DRV_PCI

x

Driver capability for PCI and EPIC controller output signals. The initial

value of this bit is determined by the PMAA2reset configuration pin.

0 High drive capability on PCI signals (25

Ω

)

1 Medium drive capability on PCI signals (50

Ω

)

6

DRV_STD

1

Driver capability for standard signals (SDA, SCL, CKO, QACK, MIV,

PMAA[0:2], and MCP).

0 High drive capability on standard signals (20

Ω

)

1 Medium drive capability on standard signals (40

Ω

)

5

DRV_MEM_CTRL_1

x

Driver capability for the MDH[0:31], MDL[0:31], PAR[0:7], MAA[0:2], and

RCS1 signals. Controlled in combination with DRV_MEM_CTRL_2, as

follows:

1 20-

Ω

data bus drive capability; when this is selected, only 8-

Ω

or

13.3-

Ω

drive capability allowed for DRV_MEM_CTRL_2

0 40-

Ω

data bus drive capability, when this is selected, only 20-

Ω

or 40-

Ω

drive capability allowed for DRV_MEM_CTRL_2

Содержание MPC8240

Страница 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Страница 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Страница 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Страница 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Страница 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Страница 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Страница 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Страница 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Страница 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Страница 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Страница 516: ...16 14 Watchpoint Trigger Applications ...

Страница 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Страница 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Страница 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...