14-8

MPC8240 Integrated Processor User’s Manual

Peripheral Logic Power Management

In doze, nap, and sleep modes, the peripheral logic always monitors the internal bus request

signal from the processor core. When it is asserted, for example due to the occurrence of

the decrementer exception, the peripheral logic exits its low power state and goes back to

the full-power state to service the request.

The MPC8240 does not support the broadcast of PCI special cycles related to low-power

operation. Thus, the PMCR1[NO_NAP_MSG] and PMCR1[NO_SLEEP_MSG] bits must

be set by initialization software (they are cleared upon reset) to indicate that the MPC8240

does not broadcast the HALT or sleep message commands on the PCI bus before entering

the nap or sleep modes, respectively.

Table 14-2 summarizes the functionality and transition criteria of the peripheral logic block

in all power states.

.

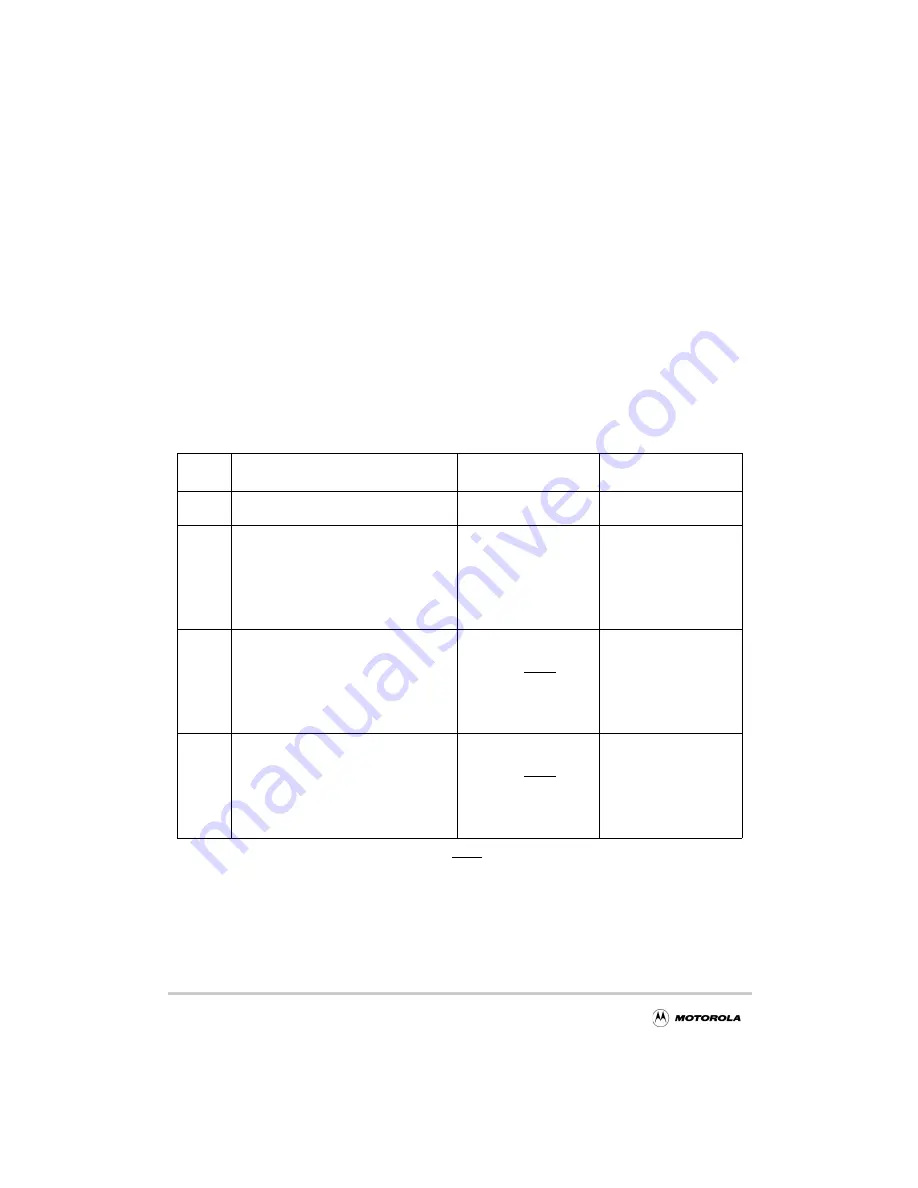

Table 14-2. Peripheral Logic Power Modes Summary

PM

Mode

Functioning Units

Activation Method

Full-Power Wake Up

Method

Full

power

All units active

—

—

Doze

PCI address decoding and bus arbiter

System RAM refreshing

Processor bus request and NMI monitoring

EPIC unit

I

2

C unit

PLL

Controlled by software

(write to PMCR1)

PCI access to memory

Processor bus request

Assertion of NMI

1

Interrupt to EPIC

Hard Reset

1

Programmable option based on value of PICR1[MCP_EN] = 1

Nap

PCI address decoding and bus arbiter

System RAM refreshing

Processor bus request and NMI monitoring

EPIC unit

I

2

C unit

PLL

Controlled by software

(write to PMCR1) and

processor core in nap or

sleep mode (QREQ

asserted)

PCI access to memory

2

Processor bus request

Assertion of NMI

Interrupt to EPIC

Hard Reset

2

A PCI access to memory in nap mode does not cause QACK to negate; consequently, it does not wake up the

processor core, and the processor core won’t snoop this access. After servicing the PCI access, the peripheral

logic automatically returns to the nap mode.

Sleep

PCI bus arbiter

System RAM refreshing (can be disabled)

Processor bus request and NMI monitoring

EPIC unit

I

2

C unit

PLL (can be disabled)

Controlled by software

(write to PMCR1) and

processor core in nap or

sleep mode (QREQ

asserted)

Processor bus request

Assertion of NMI

Interrupt to EPIC

Hard Reset

Содержание MPC8240

Страница 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Страница 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Страница 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Страница 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Страница 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Страница 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Страница 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Страница 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Страница 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Страница 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Страница 516: ...16 14 Watchpoint Trigger Applications ...

Страница 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Страница 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Страница 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...