Chapter 4. Configuration Registers

4-53

Memory Control Configuration Registers

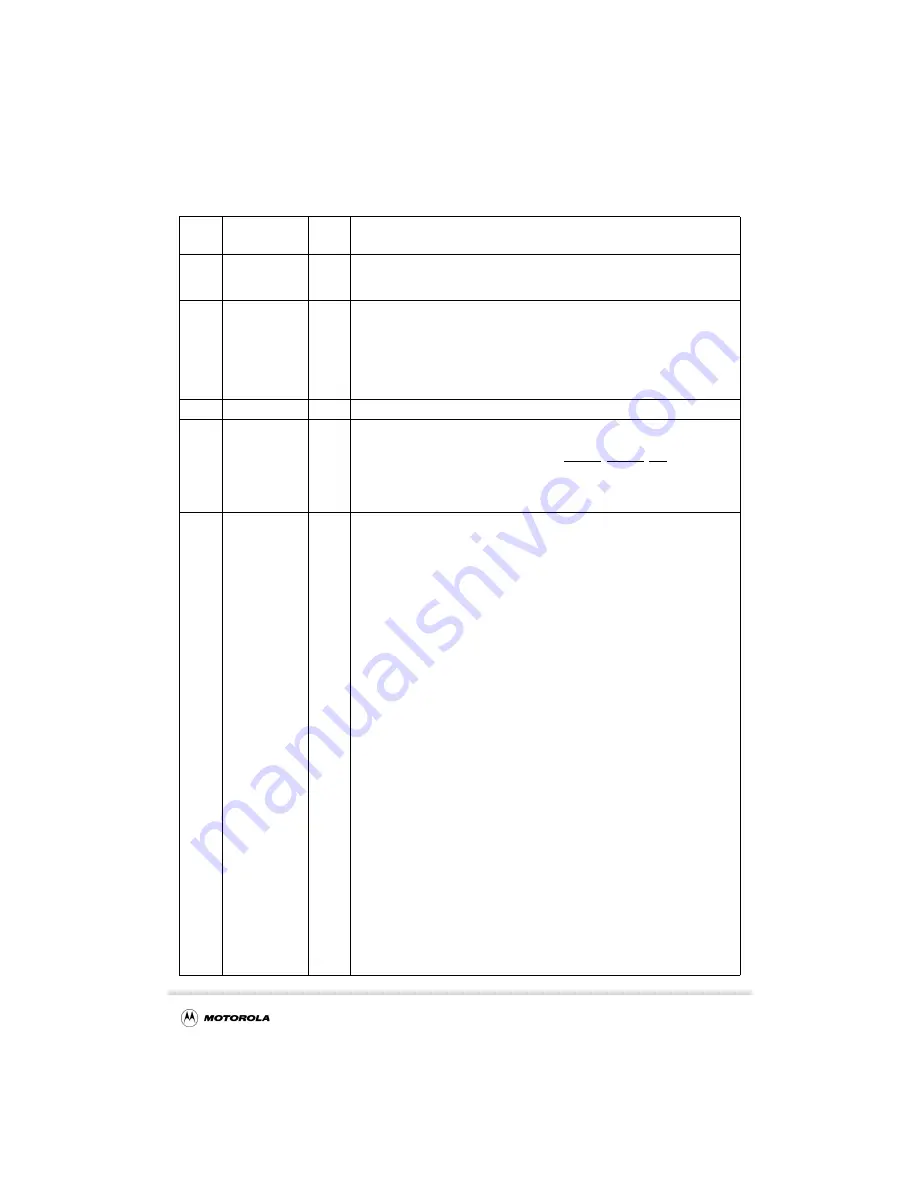

20

BUF_TYPE[1]

0

Least significant bit of the memory data bus buffer type field. BUF_TYPE[1] is

used with bit 22 above (BUF_TYPE[0]) to configure the internal memory data

path buffering scheme as described for bit 22.

19–18

BSTOPRE[0–1]

00

Burst to precharge—bits 0–1. For SDRAM only. These bits, together with

BSTOPRE[2–5] (bits 31–28 of MCCR3), and BSTOPRE[6–9] (bits 3–0 of

MCCR4), control the open page interval. The page open duration counter is

reloaded with BSTOPRE[0–9] every time the page is accessed (including page

hits). When the counter expires, the open page is closed with a

SDRAM-precharge bank command. See Chapter 6, “MPC8240 Memory

Interface,” for more information.

17–16

—

00

Reserved

15

REGDIMM

0

Registered DIMMs. Memory data and parity data path buses configured for

registered DIMMs. For SDRAM only. When enabled (REGDIMM = 1), SDRAM

write data and parity are delayed by one cycle on the memory bus with respect

to the SDRAM control signals (for example, SDRAS, SDCAS, WE).

0 Normal DIMMs

1 Registered DIMMs selected

14–8

SDMODE

All 0s

SDRAM mode register. For SDRAM only. These bits specify the SDRAM mode

register data to be written to the SDRAM array during power-up configuration.

Note that the SDRAM mode register ‘opcode’ field is not specified and is forced

to b’0_0000’ by the MPC8240 when the mode registers are written.

Bits 14–12 CAS latency

000 Reserved

001 1

010 2

011 3

100 Reserved

101 Reserved

110 Reserved

111 Reserved

Bit 11 Wrap type

0

Sequential. Default for MPC8240

1

Interleaved - Reserved

Bits 10–8 Burst length

000 Reserved

001 Reserved

010 4

011 8

100 Reserved

101 Reserved

110 Reserved

111 Reserved

Table 4-41. Bit Settings for MCCR4—0xFC (Continued)

Bits

Name

Reset

Value

Description

Содержание MPC8240

Страница 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Страница 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Страница 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Страница 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Страница 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Страница 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Страница 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Страница 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Страница 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Страница 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Страница 516: ...16 14 Watchpoint Trigger Applications ...

Страница 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Страница 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Страница 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...