Architecture

915

SPRUH22I – April 2012 – Revised November 2019

Copyright © 2012–2019, Texas Instruments Incorporated

C28 Direct Memory Access (DMA) Module

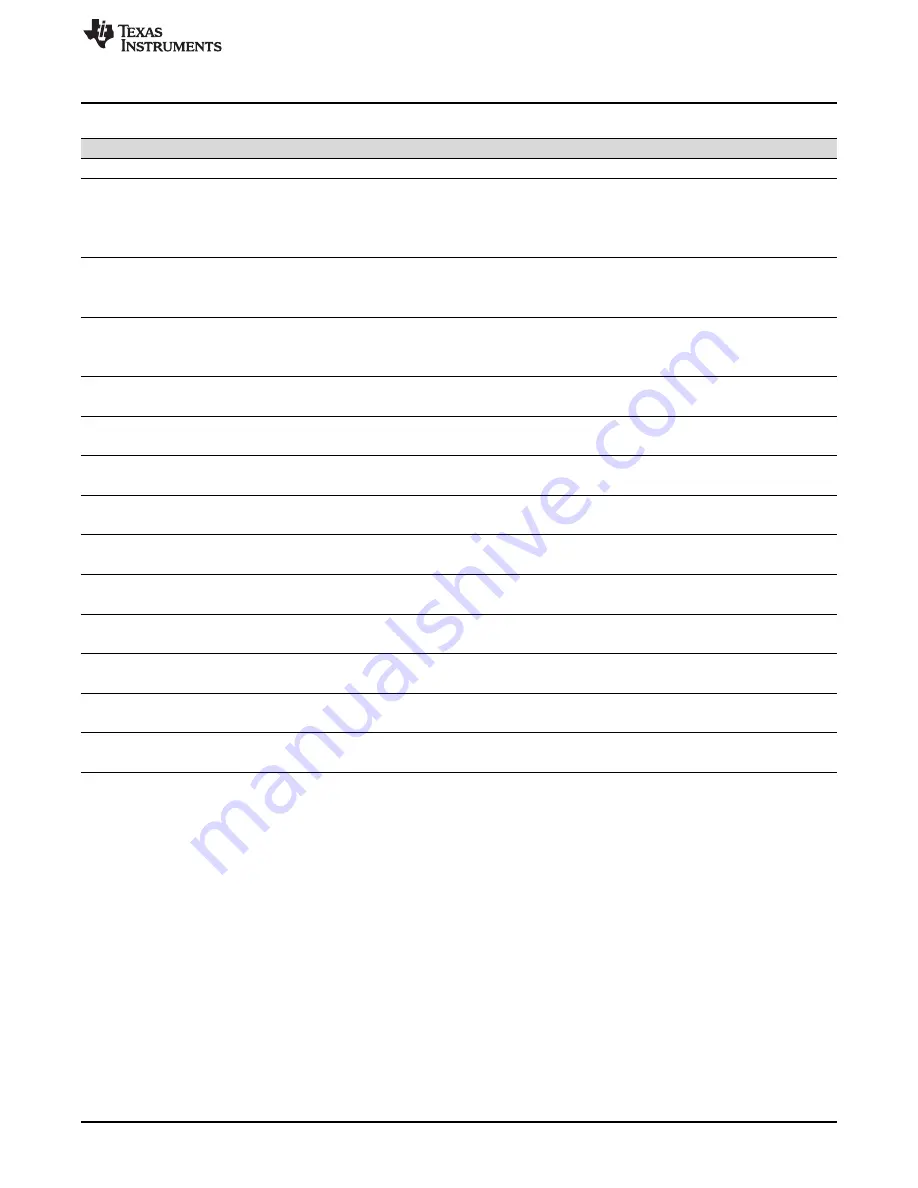

Table 11-1. Peripheral Interrupt Trigger Source Options

Peripheral

Interrupt Trigger Source

CPU

DMA Software bit (CHx.CONTROL.PERINTFRC) only

ADC

ADCINT 1

ADCINT 2

ADCINT3

ADCINT4

External Interrupts

External Interrupt 1

External Interrupt 2

External Interrupt 3

CPU Timers

Timer 0 Overflow

Timer 1 Overflow

Timer 2 Overflow

McBSP

McBSP Transmit Buffer Empty

McBSP Receive Buffer Full

ePWM1

ADC Start of Conversion A

ADC Start of Conversion B

ePWM2

ADC Start of Conversion A

ADC Start of Conversion B

ePWM3

ADC Start of Conversion A

ADC Start of Conversion B

ePWM4

ADC Start of Conversion A

ADC Start of Conversion B

ePWM5

ADC Start of Conversion A

ADC Start of Conversion B

ePWM6

ADC Start of Conversion A

ADC Start of Conversion B

ePWM7

ADC Start of Conversion A

ADC Start of Conversion B

ePWM8

ADC Start of Conversion A

ADC Start of Conversion B

ePWM9

ADC Start of Conversion A

ADC Start of Conversion B

11.2.3 DMA Bus

The DMA bus architecture consists of a 22-bit address bus, a 32-bit data read bus, and a 32-bit data write

bus. Memories and register locations connected to the DMA bus are via interfaces that sometimes share

resources with the CPU memory or peripheral bus. Arbitration rules are defined in

. The

following resources are connected to the DMA bus:

•

L2/L3 C28x local RAM

•

CTOM MSG RAM

•

MTOC MSG RAM

•

S0-S7 shared RAM

•

ADC 1 memory-mapped result registers

•

ADC 2 memory-mapped result registers

•

McBSP data receive registers (DRR2/DRR1) and data transmit registers (DXR2/DXR1)

•

ePWM1-9/HRPWM1-8 registers