Clock

Bus[7:0]

Size

R/W

Int

15:8

Int

7:0

Ready

Ready

Digital Buffer

Analog Buffer

Sync

Stall

Analog-to-Digital Converter (ADC)

859

SPRUH22I – April 2012 – Revised November 2019

Copyright © 2012–2019, Texas Instruments Incorporated

Analog Subsystem

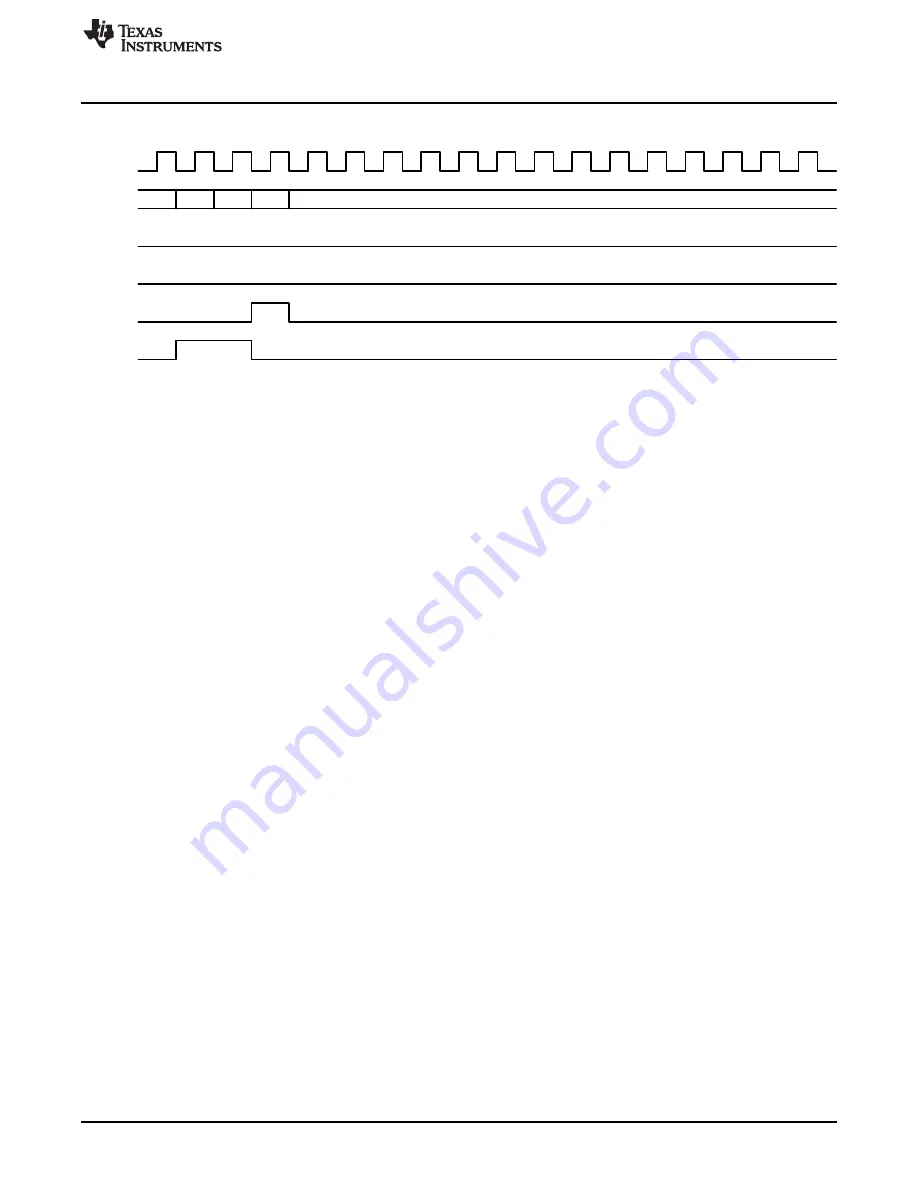

Figure 10-9. ADC Interrupt

10.3

Analog-to-Digital Converter (ADC)

The ADC module described in this reference guide is a 12-bit recyclic ADC; part SAR, part pipelined. The

analog circuits of this converter, referred to as the "core" in this document, include the front-end analog

multiplexers (MUXs), sample-and-hold (S/H) circuits, the conversion core, voltage regulators, and other

analog supporting circuits. Digital circuits, referred to as the "wrapper" in this document, include

programmable conversions, result registers, interface to analog circuits, interface to the Analog Common

Interface Bus (ACIB), and interface to other on-chip modules.

10.3.1 Features

The core of the ADC contains a single 12-bit converter fed by two sample and hold circuits. The sample

and hold circuits can be sampled simultaneously or sequentially. These, in turn, are fed by a total of up to

16 analog input channels. See the device datasheet for the specific number of channels available. The

converter can be configured to run with an internal bandgap reference to create true-voltage based

conversions or with a pair of external voltage references (VREFHI/LO) to create ratiometric based

conversions.

Contrary to previous ADC types, this ADC is not sequencer based. It is easy for the user to create a

series of conversions from a single trigger. However, the basic principle of operation is centered around

the configurations of individual conversions, called SOC’s, or start-of-conversions.

Functions of each ADC module include:

•

12-bit ADC core with built-in dual sample-and-hold (S/H)

•

Simultaneous sampling or sequential sampling modes

•

Full range analog input: 0 V to 3.3 V fixed, or VREFHI/VREFLO ratiometric

•

Up to 16-channel, multiplexed inputs

•

16 SOC’s, configurable for trigger, sample window, and channel

•

16 result registers (individually addressable) to store conversion values

•

Multiple trigger sources

–

S/W - software immediate start

–

ePWM 1-9

–

External GPIO

–

CPU Timers 0/1/2

–

ADCINT1/2

•

8 flexible PIE interrupts total for both ADC modules, can configure interrupt request after any

conversion

•

8 flexible NVIC interrupts total for both ADC modules, can configure interrupt request after any

conversion