SPI Registers and Waveforms

972

SPRUH22I – April 2012 – Revised November 2019

Copyright © 2012–2019, Texas Instruments Incorporated

C28 Serial Peripheral Interface (SPI)

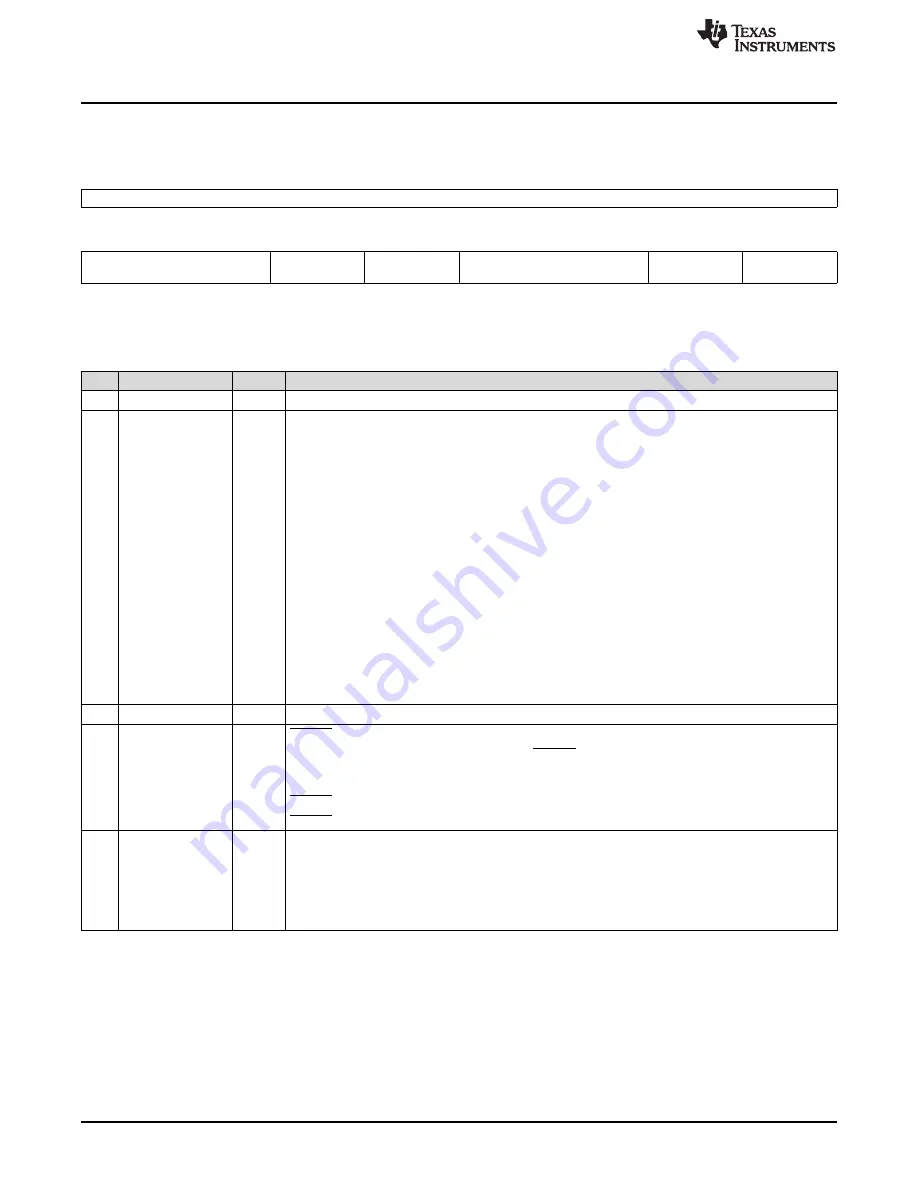

12.3.1.10 SPI Priority Control Register (SPIPRI)

Figure 12-24. SPI Priority Control Register (SPIPRI) — Address 704Fh

15

8

Reserved

R-0

7

6

5

4

3

2

1

0

Reserved

SPI SUSP

SOFT

SPI SUSP

FREE

Reserved

STEINV

TRIWIRE

R-0

R/W-0

R/W-0

R-0

R/W-0

R/W-0

LEGEND: R/W = Read/Write; R = Read only; -

n

= value after reset

Table 12-20. SPI Priority Control Register (SPIPRI) Field Descriptions

Bit

Field

Value

Description

15-6

Reserved

Reads return zero; writes have no effect.

5-4

SPI SUSP SOFT

SPI SUSP FREE

These bits determine what occurs when an emulation suspend occurs (for example, when the

debugger hits a breakpoint). The peripheral can continue whatever it is doing (free-run mode) or, if in

stop mode, it can either stop immediately or stop when the current operation (the current

receive/transmit sequence) is complete.

0 0

Transmission stops after midway in the bit stream while TSUSPEND is asserted. Once TSUSPEND

is deasserted without a system reset, the remainder of the bits pending in the DATBUF are shifted.

Example: If SPIDAT has shifted 3 out of 8 bits, the communication freezes right there. However, if

TSUSPEND is later deasserted without resetting the SPI, SPI starts transmitting from where it had

stopped (fourth bit in this case) and will transmit 8 bits from that point. The SCI module operates

differently.

1 0

If the emulation suspend occurs before the start of a transmission, (that is, before the first SPICLK

pulse) then the transmission will not occur. If the emulation suspend occurs after the start of a

transmission, then the data will be shifted out to completion. When the start of transmission occurs is

dependent on the baud rate used.

Standard SPI mode:

Stop after transmitting the words in the shift register and buffer. That is, after

TXBUF and SPIDAT are empty.

In FIFO mode:

Stop after transmitting the words in the shift register and buffer. That is, after TX FIFO

and SPIDAT are empty.

x 1

Free run, continue SPI operation regardless of suspend or when the suspend occurred.

3-2

Reserved

Reserved

1

STEINV

SPISTE inversion bit

On devices with 2 SPI modules, inverting the SPISTE signal on one of the modules allows the device

to receive left and right- channel digital audio data. This bit is only applicable to slave mode. Writing

to this bit while configured as master (MASTER_SLAVE = 1) has no effect.

0

SPISTE is active low (normal)

1

SPISTE is active high (inverted)

0

TRIWIRE

SPI 3-wire mode enable

0

Normal 4-wire SPI mode

1

3-wire SPI mode enabled. The unused pin becomes a GPIO pin. In master mode, the SPISIMO pin

becomes the SPIMOMI (master receive and transmit) pin and SPISOMI is free for non-SPI use. In

slave mode, the SIISOMI pin becomes the SPISISO (slave receive and transmit) pin and SPISIMO is

free for non-SPI use.