ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

683

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

positive edge of SPI clock.

Note:

The settings of TXNEG and RXNEG are mutual exclusive. In other words, do not transmit

and receive data at the same clock edge.

Transmit/Receive Bit Length

The bit length of a transaction word is defined in DWIDTH (SPIn_CTL[12:8]) and can be configured

up to 32-bit length in a transaction word for transmitting and receiving.

When SPI controller finishes a transaction, i.e. receives or transmits a specific count of bits defined

in DWIDTH (SPIn_CTL[12:8]), the unit transfer interrupt flag will be set to 1.

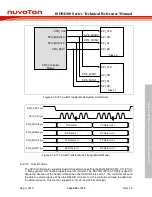

SPIx_CLK pin

SPIx_MOSIz pin

SPIx_MISOz pin

TX[30]

TX[16]

TX[15] TX[14]

LSB

TX[0]

RX[30]

RX[16]

RX[14]

LSB

RX[0]

MSB

RX[31]

RX[15]

MSB

TX[31]

SPIx_SSy pin

Note:

x: Controller number (x = 0, 1, 2), y: Slave selection pin channel number in SPI0 (y = 0, 1),

z: MOSI and MISO pin channel number in SPI0 (z = 0)

Figure 6.14-9 32-Bit in One Transaction

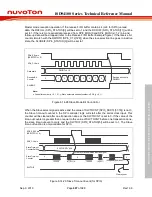

LSB/MSB First

LSB (SPIn_CTL[13]) defines the bit transfer sequence in a transaction. If the LSB (SPIn_CTL[13])

is set to 1, the transfer sequence is LSB first. The bit 0 will be transferred firstly. If the LSB

(SPIn_CTL[13]) is cleared to 0, the transfer sequence is MSB first.

Suspend Interval

SUSPITV (SPIn_CTL[7:4]) provides a configurable suspend interval, 0.5 ~ 15.5 SPI clock periods,

between two successive transaction words in Master mode. The definition of the suspend interval

is the interval between the last clock edge of the preceding transaction word and the first clock edge

of the following transaction word. The default value of SUSPITV is 0x3 (3.5 SPI clock cycles).

6.14.5.2 Automatic Slave Selection

In Master mode, if AUTOSS (SPIn_SSCTL[3]) is set, the slave selection signal will be generated

automatically and output to the slave selection pin according to whether SS (SPIn_SSCTL[0]) and

SS1 (SPI0_SSCTL[1]) is enabled or not. The slave selection signal will be set to active state by the

SPI controller when the SPI data transfer is started by writing to FIFO. It will be set to inactive state

when SPI bus is idle. If SPI bus is not idle, i.e. TX FIFO, TX shift register or TX skew buffer is not

empty, the slave selection signal will be set to inactive state between transactions if the value of

Содержание ISD94100 Series

Страница 528: ...ISD94100 Series Technical Reference Manual Sep 9 2019 Page 528 of 928 Rev1 09 ISD94100 SERIES TECHNICAL REFERENCE MANUAL...

Страница 626: ...ISD94100 Series Technical Reference Manual Sep 9 2019 Page 626 of 928 Rev1 09 ISD94100 SERIES TECHNICAL REFERENCE MANUAL...

Страница 702: ...ISD94100 Series Technical Reference Manual Sep 9 2019 Page 702 of 928 Rev1 09 ISD94100 SERIES TECHNICAL REFERENCE MANUAL...

Страница 875: ...ISD94100 Series Technical Reference Manual Sep 9 2019 Page 875 of 928 Rev1 09 ISD94100 SERIES TECHNICAL REFERENCE MANUAL...