ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

346

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

continuous counting operation modes.

Timer input clock or event source is divided by (PSC+1) before it is fed to the 24 bit up counter. By

default the 8-bit prescaler PSC (TIMERx_CTL[7:0]) value is 0.

6.7.5.3

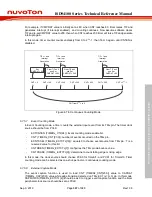

One–shot Mode

Writing 0b00 into TIMERx_CTL[28:27] selects one-shot mode for that timer.

CNTEN (TIMERx_CTL[30]) is the timer enable bit. Once enabled, the timer counter starts up

counting. Once the CNT (TIMERx_CNT[23:0]) value reaches CMPDAT (TIMERx_CMP[23:0]), TIF

(TIMERx_INTSTS[0]) will be set to 1, CNT value and CNTEN bit is automatically cleared by

hardware and timer counting operation stops. A timer interrupt will be triggered if INTEN

(TIMERx_CTL[29]) is enabled.

Software can monitor bit RSTACT (TIMERx_CNT[31]) to judge if the counter reset operation is still

in progress. active by. Software can also set ICEDEBUG (TIMERx_CTL[31]) to 1 that disable ICE

debug mode acknowledgement if found affecting TIMER counting.

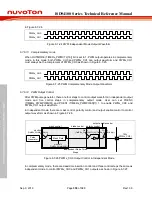

6.7.5.4

Periodic Mode

Writing 0b01 into TIMERx_CTL[28:27] selects periodic mode for that timer.

CNTEN (TIMERx_CTL[30]) is the timer enable bit. Once enabled, the timer counter starts to count.

Once the CNT (TIMERx_CNT[23:0]) value reaches CMPDAT (TIMERx_CMP[23:0]), TIF

(TIMERx_INTSTS[0]) will be set to 1, CNT value will be automatically cleared by hardware and

timer counter start to count from 0 again. In the meantime, if INTEN (TIMERx_CTL[29]) is enabled

a timer interrupt will be generated.

In this mode, timer controller keeps counting and comparing with CMPDAT value continuously,

raises TIF periodically until the CNTEN bit is cleared.

6.7.5.5

Toggle-Output Mode

Writing 0b10 into TIMERx_CTL[28:27] selects toggle-output mode.

Under toggle-output mode, timer starts up counting once CNTEN (TIMERx_CTL[30]) is enabled.

when the CNT (TIMERx_CNT[23:0]) value reaches CMPDAT (TIMERx_CMP[23:0]), device toggles

the output signal on associated TM0/1/2/3 pin; for example, Timer0 associated toggle-output pin is

TM0. Also device raises TIF flag.

In this mode, the timer continuously counts, periodically toggles the output on the TMx pin and

raises TIF (hence interrupt will be generated if interrupt enabled), until CNTEN bit is cleared. The

duty cycle on TMx pin is 50%.

6.7.5.6

Continuous Counting Mode

Writing 0b11 into TIMERx_CTL[28:27] selects continuous counting mode.

Under continuous counting mode, timer starts up counting once CNTEN (TIMERx_CTL[30]) is

enabled.

When CNT (TIMERx_CNT[23:0]) value reaches CMPDAT (TIMERx_CMP[23:0]) value, the TIF

(TIMERx_INTSTS[0]) will be set to 1, hence a timer interrupt generated if enabled, and counting

continues. Software can change CMPDAT to a different value immediately without

stopping/resetting timer.

Содержание ISD94100 Series

Страница 528: ...ISD94100 Series Technical Reference Manual Sep 9 2019 Page 528 of 928 Rev1 09 ISD94100 SERIES TECHNICAL REFERENCE MANUAL...

Страница 626: ...ISD94100 Series Technical Reference Manual Sep 9 2019 Page 626 of 928 Rev1 09 ISD94100 SERIES TECHNICAL REFERENCE MANUAL...

Страница 702: ...ISD94100 Series Technical Reference Manual Sep 9 2019 Page 702 of 928 Rev1 09 ISD94100 SERIES TECHNICAL REFERENCE MANUAL...

Страница 875: ...ISD94100 Series Technical Reference Manual Sep 9 2019 Page 875 of 928 Rev1 09 ISD94100 SERIES TECHNICAL REFERENCE MANUAL...