ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

435

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

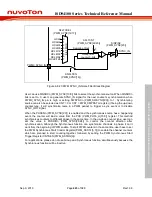

if the input channel has a rising transition or a falling transition, respectively. The capture function

will also generate an interrupt CAP_INT (using PWM_INT vector) if the rising or falling latch occurs

and the corresponding channel n’s rising or falling interrupt enable bits are set, where the

CAPRIENn (PWM_CAPIEN[5:0]) bit is for the rising edge and the CAPFIENn

(PWM_CAPIEN[13:8]) bit is for the falling edge. When rising or falling latch occurs, the

corresponding PWM counter may be reloaded with the value of PWM_PERIODn register,

depending on the setting of RCRLDENn or FCRLDENn bits (where RCRLDENn and FCRLDENn

are located at PWM_CAPCTL[21:16] and PWM_CAPCTL[29:24], respectively). Note that the

corresponding GPIO pins must be configured as the capture function by enable the CAPINENn

(PWM_CAPINEN[5:0]) bits for the corresponding capture channel n. Figure 6.8-40 is the capture

block diagram of channel 0.

0

1

16-bits PWM

up/down counter

CNT

(PWM_CNT0[15:0])

DIRF

(PWM_CNT0[16])

PERIOD

(PWM_PERIOD0)

RCAPDAT

(PWM_RCAPDAT0[15:0])

FCAPDAT

(PWM_FCAPDAT0[15:0])

CAPEN0

(PWM_CAPCTL[0])

CAPINV0

(PWM_CAPCTL[8])

CAPINEN0

(PWM_CAPINEN[0])

PWM_CH0

RCRLDEN0

(PWM_CAPCTL[16])

FCRLDEN0

(PWM_CAPCTL[24])

Note:

denotes rising edge detect

denotes falling edge detect

Rising Latch

Falling Latch

Figure 6.8-40 PWM0_CH0 Capture Block Diagram

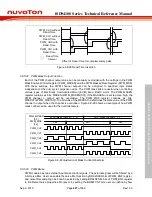

Figure 6.8-41 illustrates the capture function timing. In this case, the capture counter is set as PWM

down counter type and the PERIOD is set to 8 so that the counter counts in the down direction,

from 8 to 0. When detecting a falling edge at the capture input pin, the capture function latches the

counter value to the PWM_FCAPDATn register. When detecting the rising edge, it latches the

counter value to the PWM_RCAPDATn register. In this timing diagram, when the falling edge is

detected at the first time, the capture function will reload the counter value from the PERIOD setting

because the FCRLDENn bit is enabled. But at the second time, the falling edge does not result in

a reload because of the disabled FCRLDENn bit. In this example, the counter also reloads at the

rising edge of the capture input because the RCRLDENn bit is enabled, too.

Moreover, if the case is setup as the up counter type, the counter will reload the value zero and

count up to the value PERIOD.

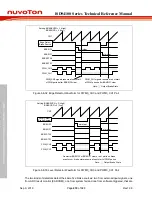

Figure 6.8-41 also illustrates the timing example for the interrupt and interrupt flag generation. When

Содержание ISD94100 Series

Страница 528: ...ISD94100 Series Technical Reference Manual Sep 9 2019 Page 528 of 928 Rev1 09 ISD94100 SERIES TECHNICAL REFERENCE MANUAL...

Страница 626: ...ISD94100 Series Technical Reference Manual Sep 9 2019 Page 626 of 928 Rev1 09 ISD94100 SERIES TECHNICAL REFERENCE MANUAL...

Страница 702: ...ISD94100 Series Technical Reference Manual Sep 9 2019 Page 702 of 928 Rev1 09 ISD94100 SERIES TECHNICAL REFERENCE MANUAL...

Страница 875: ...ISD94100 Series Technical Reference Manual Sep 9 2019 Page 875 of 928 Rev1 09 ISD94100 SERIES TECHNICAL REFERENCE MANUAL...