ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

404

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

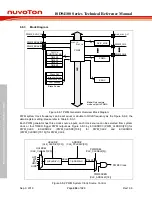

6.8.3

Block Diagram

APB

PWM0

PWM0_BRAKE0

PWM0_BRAKE1

PWM0_SYNC_IN

SYNC_IN

SYNC_OUT

TIMER0

EADC

CLOCK

CONTROLLER

5

TIMER1

TIMER2

TIMER3

PDMA

PWM0_CH0

PWM0_CH5

4

NVIC_MUX

3

6

Note:

Only capture

mode output to PDMA

Clock Fail

Brown-Out Detect

SRAM Parity Error

CPU Lockup

Brake Source

4

PWM0_SYNC_OUT

Figure 6.8-1 PWM Generator Overview Block Diagram

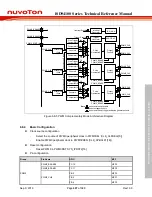

PWM system clock frequency can be set equal or double to HCLK frequency as the Figure 6.8-2, the

detail register setting, please refer to Table 6.8.3-1.

Each PWM generator has three clock source inputs, each clock source can be selected from system

clock or four TIMER trigger PWM outputs as Figure 6.8-3 by ECLKSRC0 (PWM_CLKSRC[2:0]) for

PWM_CLK0, ECLKSRC2 (PWM_CLKSRC[10:8]) for PWM_CLK2 and ECLKSRC4

(PWM_CLKSRC[18:16]) for PWM_CLK4.

HCLKSEL

(CLK_CLKSEL0[2:0])

1/(1)

HCLK

1

0

PWM0 Clock

PCLK0

PWM0SEL

(CLK_CLKSEL2[0])

PWM0CKEN

(CLK_APBCLK1[16])

HCLKDIV

(CLK_CLKDIV0[3:0])

0

1

2

3

7

HXT

LXT

PLL

LIRC

HIRC

1/(1)

APB0DIV

(CLK_PCLKDIV[3:0])

Figure 6.8-2 PWM System Clock Source Control

Содержание ISD94100 Series

Страница 528: ...ISD94100 Series Technical Reference Manual Sep 9 2019 Page 528 of 928 Rev1 09 ISD94100 SERIES TECHNICAL REFERENCE MANUAL...

Страница 626: ...ISD94100 Series Technical Reference Manual Sep 9 2019 Page 626 of 928 Rev1 09 ISD94100 SERIES TECHNICAL REFERENCE MANUAL...

Страница 702: ...ISD94100 Series Technical Reference Manual Sep 9 2019 Page 702 of 928 Rev1 09 ISD94100 SERIES TECHNICAL REFERENCE MANUAL...

Страница 875: ...ISD94100 Series Technical Reference Manual Sep 9 2019 Page 875 of 928 Rev1 09 ISD94100 SERIES TECHNICAL REFERENCE MANUAL...