•

Double TLB miss (MMU only)

•

TLB permission violation (MMU only)

•

MPU region violation (MPU only)

5.2.9.1. External Interrupt Controller Interface

The EIC interface enables you to speed up interrupt handling in a complex system by

adding a custom interrupt controller.

The EIC interface is an Avalon-ST sink with the following input signals:

•

eic_port_valid

•

eic_port_data

Signals are rising-edge triggered, and synchronized with the Nios II clock input.

The EIC interface presents the following signals to the Nios II processor through the

eic_port_data

signal:

•

Requested handler address (RHA)—The 32-bit address of the interrupt handler

associated with the requested interrupt.

•

Requested register set (RRS)—The six-bit number of the register set associated

with the requested interrupt.

•

Requested interrupt level (RIL)—The six-bit interrupt level. If RIL is 0, no interrupt

is requested.

•

Requested nonmaskable interrupt (RNMI) flag—A one-bit flag indicating whether

the interrupt is to be treated as nonmaskable.

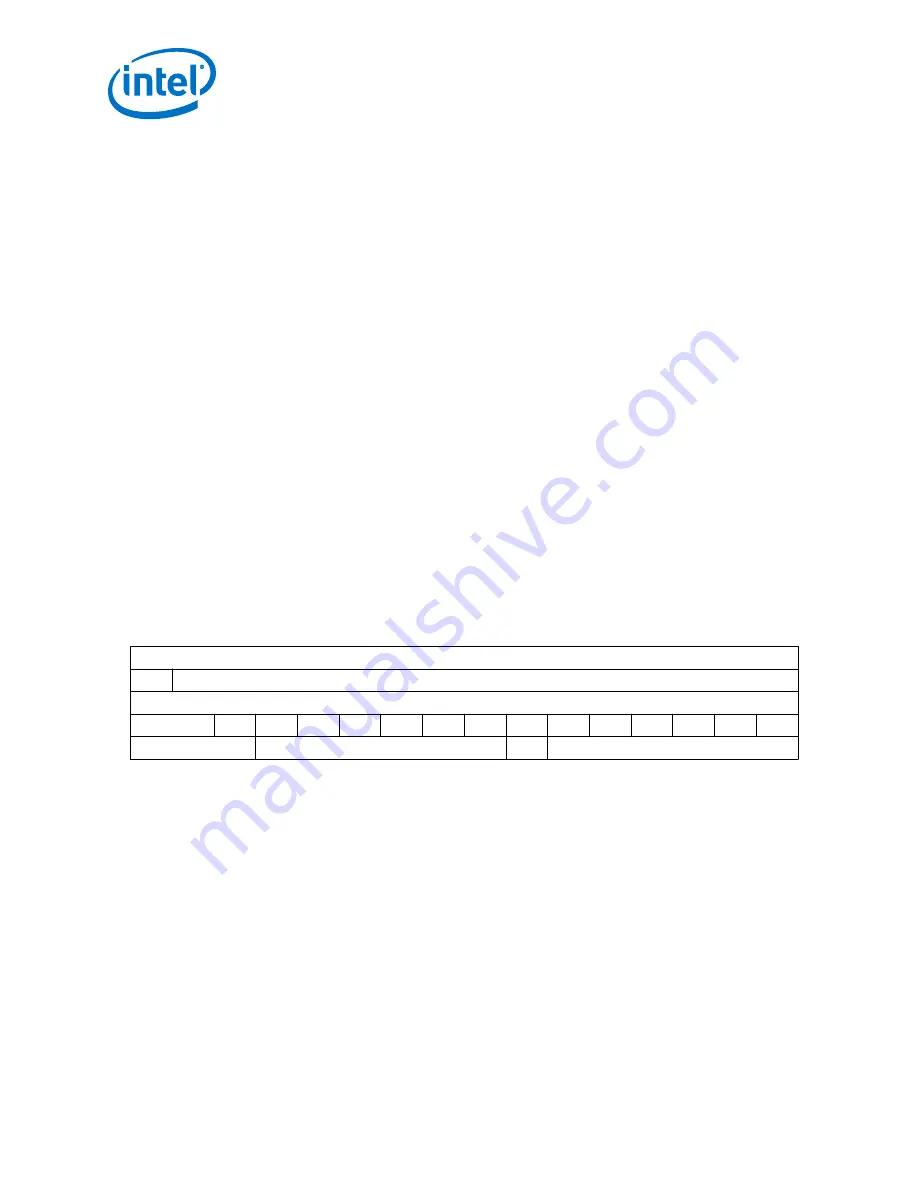

Table 69.

eic_port_data Signal

Bit Fields

44

...

RHA

...

13

12

11

10

9

8

7

6

5

4

3

2

1

0

RHA

RRS

RNMI

RIL

Following Avalon-ST protocol requirements, the EIC interface samples

eic_port_data

only when

eic_port_valid

is asserted (high). When

eic_port_valid

is not asserted, the processor latches the previous values of RHA,

RRS, RIL and RNMI. To present new values on

eic_port_data

, the EIC must

transmit a new packet, asserting

eic_port_valid

. An EIC can transmit a new

packet once per clock cycle.

For an example of an EIC implementation, refer to the Vectored Interrupt Controller

chapter in the Embedded Peripherals IP User Guide.

Related Information

Embedded Peripherals IP User Guide

5. Nios II Core Implementation Details

NII-PRG | 2018.04.18

Nios II Processor Reference Guide

132