Functional Description

603

SLAU723A – October 2017 – Revised October 2018

Copyright © 2017–2018, Texas Instruments Incorporated

Micro Direct Memory Access (µDMA)

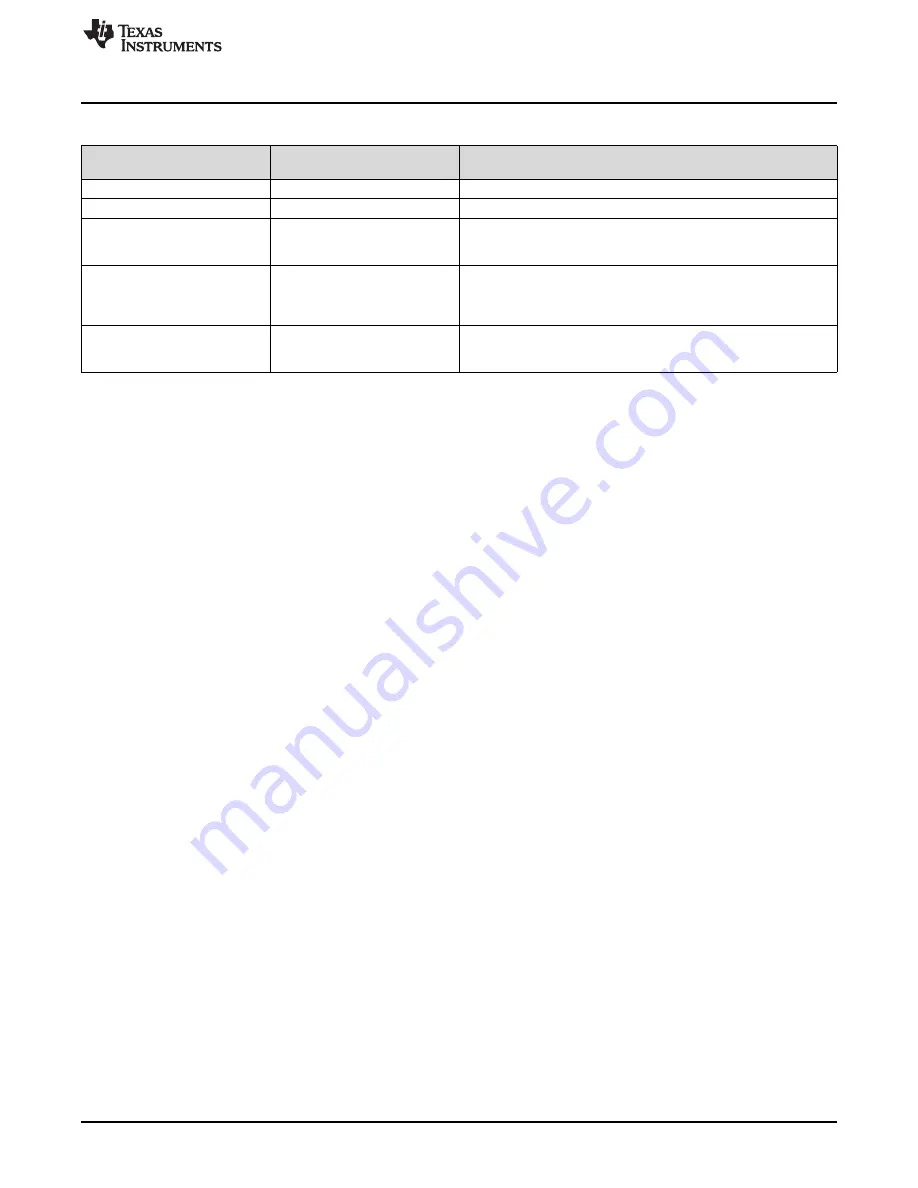

Table 8-1. Request Type Support (continued)

Peripheral

Event That Generates Single

Request

Event That Generates Burst Request

UART TX

TX FIFO not full

TX FIFO level (configurable)

UART RX

RX FIFO not empty

RX FIFO level (configurable)

SHA/MD5

None

Context in DMA request (SHA/MD5 0 Cin)

Context out DMA request (SHA/MD5 0 Cout)

Data In DMA request (SHA/MD5 0 Din)

AES

None

Context in DMA request (AES0 Cin)

Context out DMA request (AES0 Cout)

Data in DMA request (AES0 Din)

Data out DMA request (AES0 Dout)

DES

None

Context in DMA request (DES0 Cin)

Data in DMA request (DES0 Din)

Data out DMA request (DES0 Dout)

8.3.3.1

Single Request

When a single request is detected, and not a burst request, the µDMA controller transfers one item and

then stops to wait for another request.

8.3.3.2

Burst Request

When a burst request is detected, the µDMA controller transfers the number of items that is the lesser of

the arbitration size or the number of items remaining in the transfer. Therefore, the arbitration size should

be the same as the number of data items that the peripheral can accommodate when making a burst

request. For example, the UART generates a burst request based on the FIFO trigger level. In this case,

the arbitration size should be set to the amount of data that the FIFO can transfer when the trigger level is

reached. A burst transfer runs to completion once it is started, and cannot be interrupted, even by a higher

priority channel. Burst transfers complete in a shorter time than the same number of non-burst transfers.

It may be desirable to use only burst transfers and not allow single transfers. For example, perhaps the

nature of the data is such that it only makes sense when transferred together as a single unit rather than

one piece at a time. The single request can be disabled by using the DMA Channel Useburst Set

(DMAUSEBURSTSET) register. By setting the bit for a channel in this register, the µDMA controller only

responds to burst requests for that channel.

8.3.4 Channel Configuration

The µDMA controller uses an area of system memory to store a set of channel control structures in a

table. The control table may have one or two entries for each µDMA channel. Each entry in the table

structure contains source and destination pointers, transfer size, and transfer mode. The control table can

be located anywhere in system memory, but it must be contiguous and aligned on a 1024-byte boundary.

lists the layout in memory of the channel control table. Each channel may have one or two

control structures in the control table: a primary control structure and an optional alternate control

structure. The table is organized so that all of the primary entries are in the first half of the table, and all

the alternate structures are in the second half of the table. The primary entry is used for simple transfer

modes where transfers can be reconfigured and restarted after each transfer is complete. In this case, the

alternate control structures are not used and therefore only the first half of the table must be allocated in

memory; the second half of the control table is not necessary, and that memory can be used for

something else. If a more complex transfer mode is used such as ping-pong or scatter-gather, then the

alternate control structure is also used and memory space should be allocated for the entire table.

Any unused memory in the control table may be used by the application. This includes the control

structures for any channels that are unused by the application as well as the unused control word for each

channel.