12

IBM

Eserver

xSeries 455 Planning and Installation Guide

Specifically, in today's 32-bit processors, much of the instruction scheduling

(the order in which computing instructions are executed) is done on the chip

itself, leading to a great deal of overhead and slowing down overall processor

performance. Moreover, today's processors are plagued by instruction flow

problems since the processor often has to stop what it is doing and

reconstruct the instruction flow due to inherent inefficiencies in instruction

handling.

EPIC makes the instruction scheduling more intelligent and handles much of

the scheduling off-chip, in the compiler program, before feeding “parallelized”

instructions to the Itanium 2 processor for execution. The parallelized

instructions allow the chip to process a number of instructions simultaneously,

increasing performance.

The Itanium 2 architecture is based on EPIC technology and has the following

features:

– Provides faster online transaction processing

– Has the capability to execute multiple instructions simultaneously

– Enables faster calculations and data analysis

– Allows for faster storage and movement of large models (CAD, CAE)

– Speeds up simulation and rendering times

For more information about the features of the Itanium 2 processor, go to:

http://www.intel.com/design/itanium2

IBM XceL4 Accelerator Cache

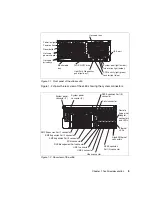

Integrated into the processor-board assembly is 64 MB of Level 4 cache, which is

shown in Figure 1-4 on page 8. This XceL4 Server Accelerator Cache provides

the necessary extra level of cache to maximize CPU throughput by reducing the

need for main memory access under demanding workloads, resulting in an

overall enhancement to system performance.

Cache memory is two-way interleaved 200 MHz DDR memory and is faster than

the main memory because it is directly connected to the Cache and Scalability

Controller and does not have additional latency associated with the large fan-out

necessary to support the 28 DIMM slots. Since the data interface to the controller

is 400 MHz, peak bandwidth for the XceL4 cache is 6.4 GBps.

The XceL4 Accelerator Cache has been designed with commercial workloads in

mind that tend to have high cache hit rates. This effectively boosts performance

and compensates in part for the 3.2 GBps bandwidth between the Cache and

Scalability Controller and Memory Controller.

Summary of Contents for 88553RX

Page 2: ......

Page 214: ...200 IBM Eserver xSeries 455 Planning and Installation Guide Figure 5 14 Connect to the x455...

Page 228: ...214 IBM Eserver xSeries 455 Planning and Installation Guide...

Page 229: ...IBM Eserver xSeries 455 Planning and Installation Guide...

Page 230: ......

Page 231: ......